Integrated circuit layout method

A technology of integrated circuits and layout methods, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve problems such as rising leakage, not necessarily good results, and time-consuming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] The terms used in the following explanations refer to the customary terms in the technical field. If some terms are explained or defined in this manual, the explanations of these terms shall be based on the descriptions or definitions in this manual.

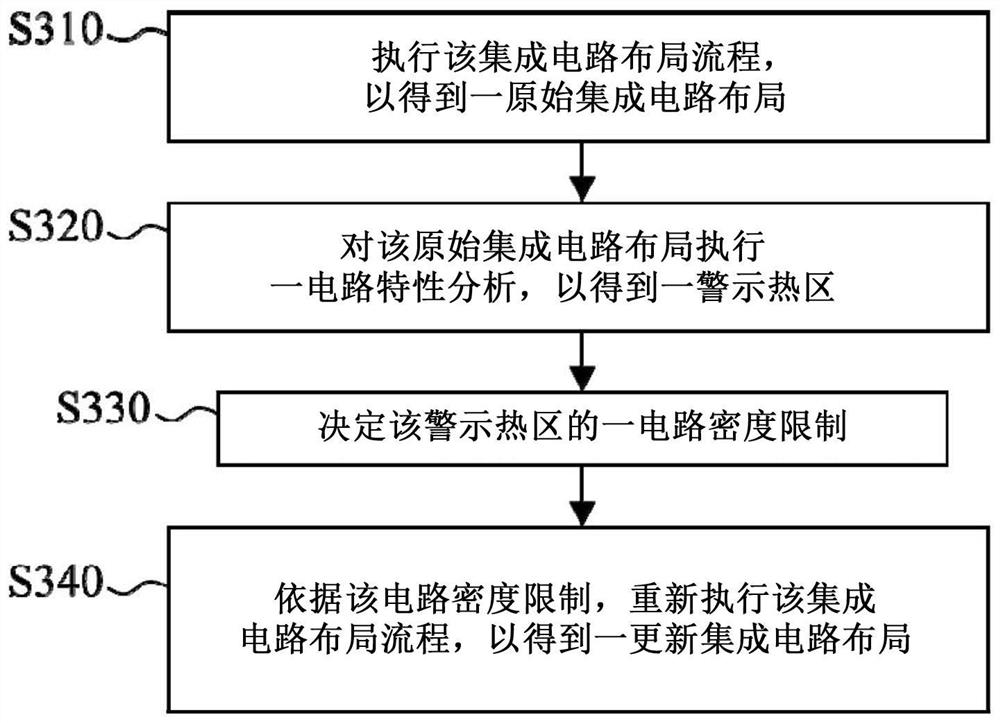

[0013] The invention discloses an integrated circuit layout method, which can improve the circuit characteristics of the result of an integrated circuit layout process, and can reduce manpower intervention, so as to improve and speed up the integrated circuit layout process. The present invention is applicable to the design process of an application-specific integrated circuit (ASIC) or other types of integrated circuits, and is especially suitable for the design of integrated circuits (such as: high-speed and low-power integrated circuits) sensitive to potential drop (IR Drop) process; however, the application of the present invention is not limited thereto.

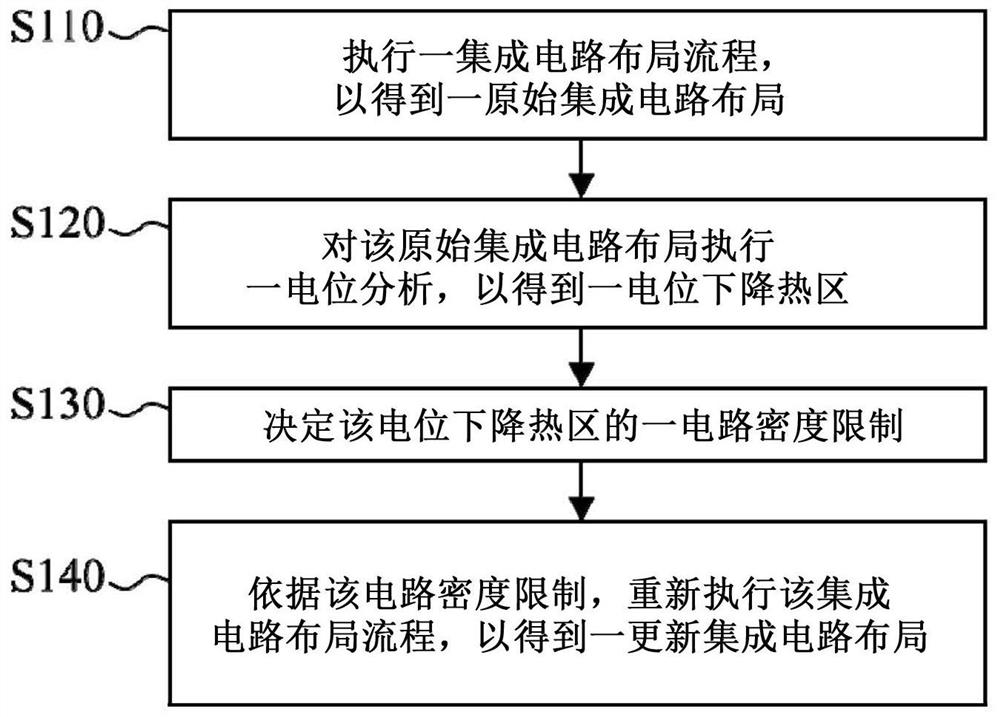

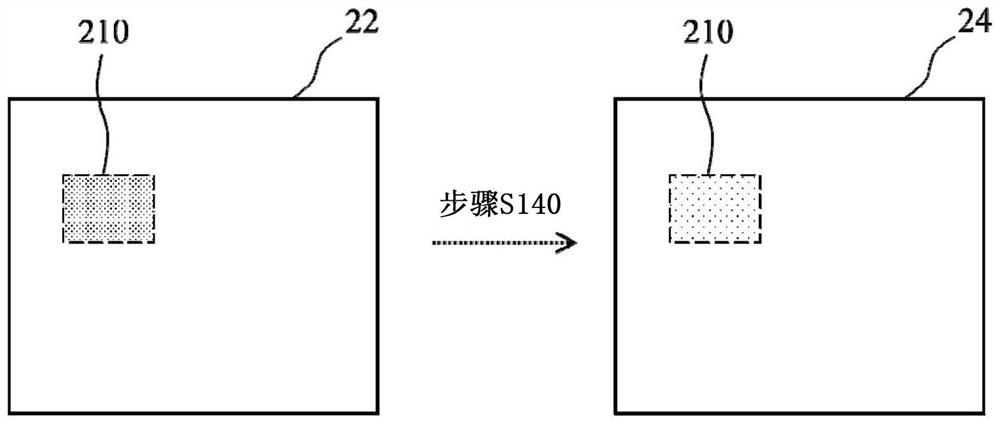

[0014] figure 1 An embodiment of the integrated circuit layo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com