Method for reducing damage to IO interface of packaged chip

A technology for mounting chips and interfaces, applied in the field of reducing damage to the IO interface of packaged chips, can solve the problems of reducing the yield rate of packaged chips, long etching time, and easily damaged IO interfaces of chips, so as to reduce the damage of IO interfaces of chips, improve production efficiency, The effect of accelerating the hole opening efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

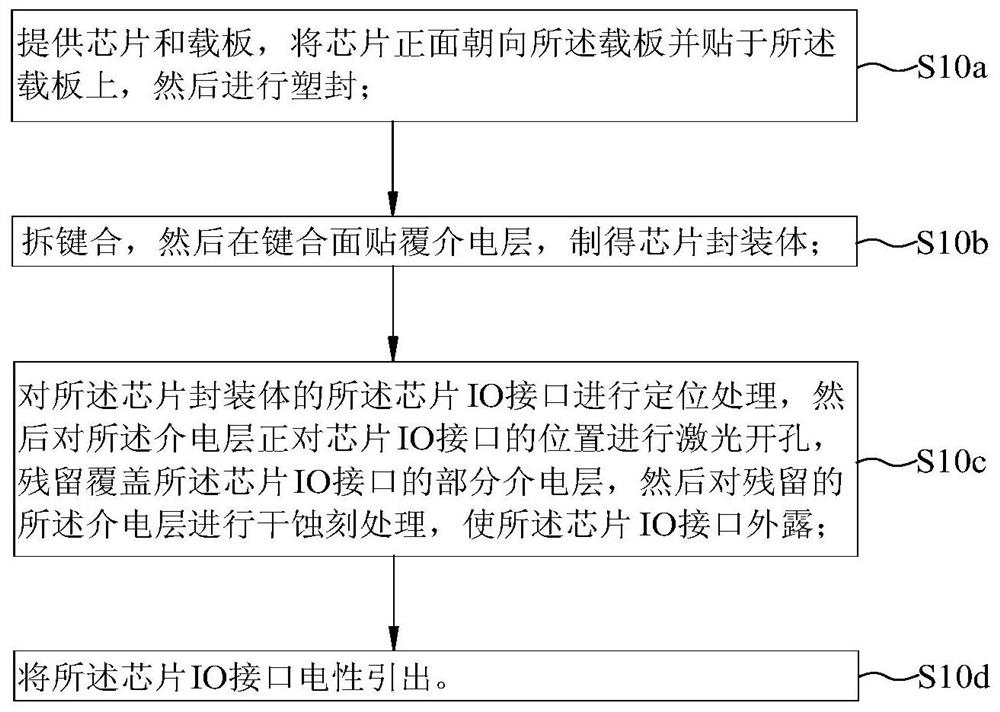

[0058] Such as figure 1 As shown, in this embodiment, the method for reducing the damage to the IO interface of the packaged chip includes the following steps:

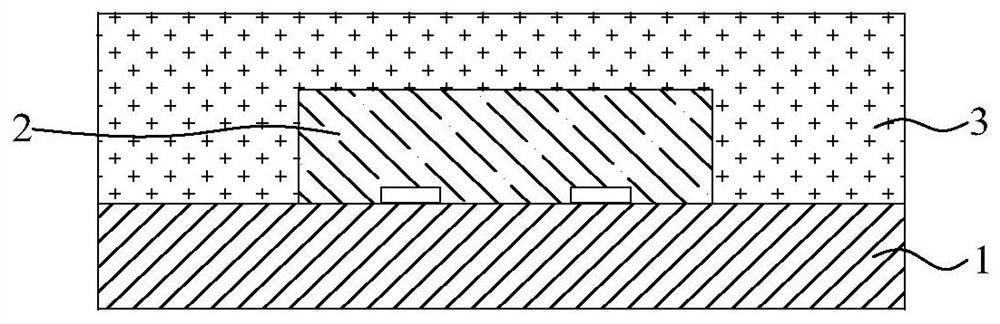

[0059] S10a, providing the chip 2 and the carrier 1, facing the front of the chip 2 to the carrier 1 and pasting it on the carrier 1, and then performing plastic packaging to form a plastic sealing layer 3 covering the chip 2 ( figure 2 );

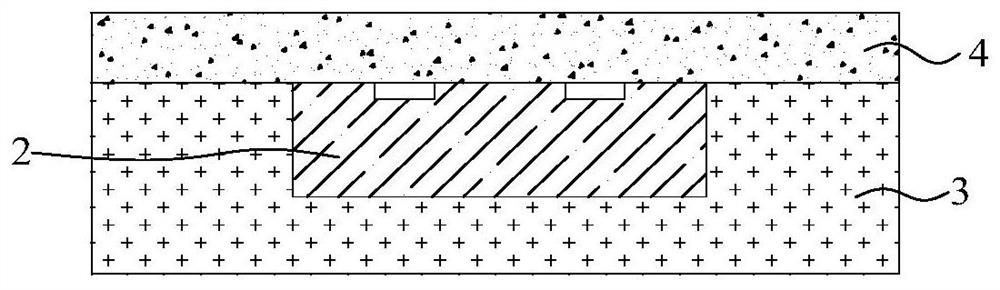

[0060] S10b, dismantling and bonding, turning over, and then sticking a dielectric layer 4 on the bonding surface, making the following image 3 The chip package shown;

[0061] S10c, performing positioning processing on the chip IO interface of the chip package, and then performing laser opening on the position of the dielectric layer 4 facing the chip IO interface ( Figure 4 ), control the laser opening speed and laser opening time, and leave a dielectric layer (residual dielectric layer 41) covering the IO interface of the chip with a thickness of 1-2 μm, and then remove t...

Embodiment 2

[0064] Such as Figure 6 As shown, in this embodiment, the method for reducing the damage to the IO interface of the packaged chip includes the following steps:

[0065] S20a, providing the chip 20 and the carrier 10, the back of the chip 20 faces the carrier 10 and sticks it on the carrier 10, and then performs plastic sealing to form a plastic sealing layer 30 covering the chip 20 ( Figure 7 );

[0066] S20b, performing grinding and thinning treatment on the plastic encapsulation layer 30, and then attaching the dielectric layer 40 to obtain a chip package ( Figure 8 );

[0067] S20c, performing positioning processing on the chip IO interface of the chip package, and then performing laser drilling on the position of the dielectric layer 40 facing the chip IO interface, controlling the laser opening speed and laser opening time, and remaining A dielectric layer (residual dielectric layer 401) covering the IO interface of the chip with a thickness of 1-2 μm ( Figure 9 )...

Embodiment 3

[0070] Such as Figure 11 As shown, in this embodiment, the method for reducing the damage to the IO interface of the packaged chip includes the following steps:

[0071] S30a, providing the chip 200 and the carrier 100, the back of the chip 200 facing the carrier 100 and affixed on the carrier 100, and then performing plastic packaging to form a plastic sealing layer 300 covering the chip 200, and the following is obtained: Figure 12 The chip package shown;

[0072] S30b, performing positioning processing on the chip IO interface of the chip package, and then performing laser opening on the position of the plastic sealing layer 300 facing the chip IO interface, controlling the laser opening speed and laser opening time, and remaining thickness The plastic sealing layer (residual plastic sealing layer 3001) covering the IO interface of the chip is 1-2 μm ( Figure 13 ), and then carry out dry etching treatment on the residual plastic encapsulation layer 3001, so that the IO...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com