A Legalization Method of FPGA Layout Based on Maximum Flow Algorithm

A most streamlined and legal technology, applied in the field of FPGA, can solve problems such as inability to take into account layout quality, lack of orientation, unsatisfactory solutions, etc., to achieve the effect of excellent layout results, better layout results, and improved quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

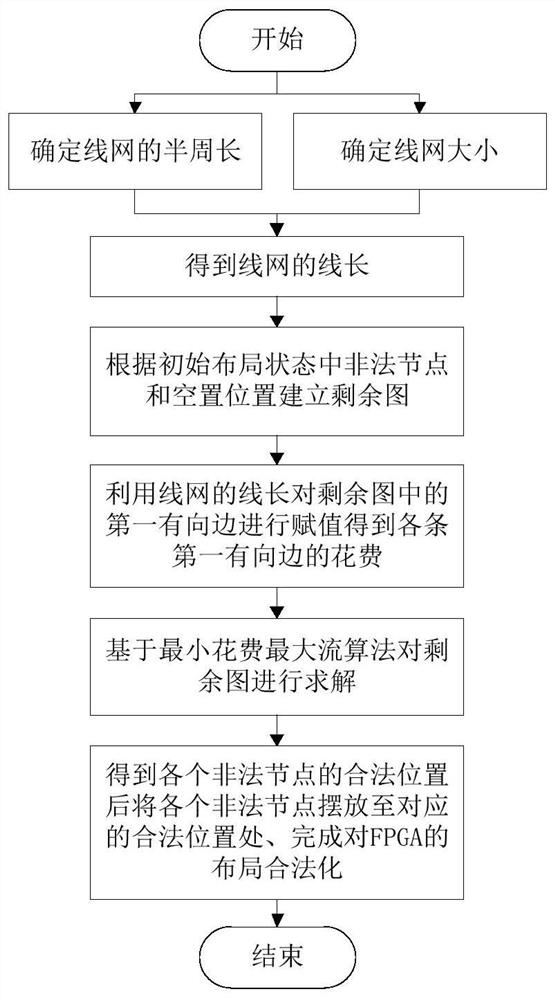

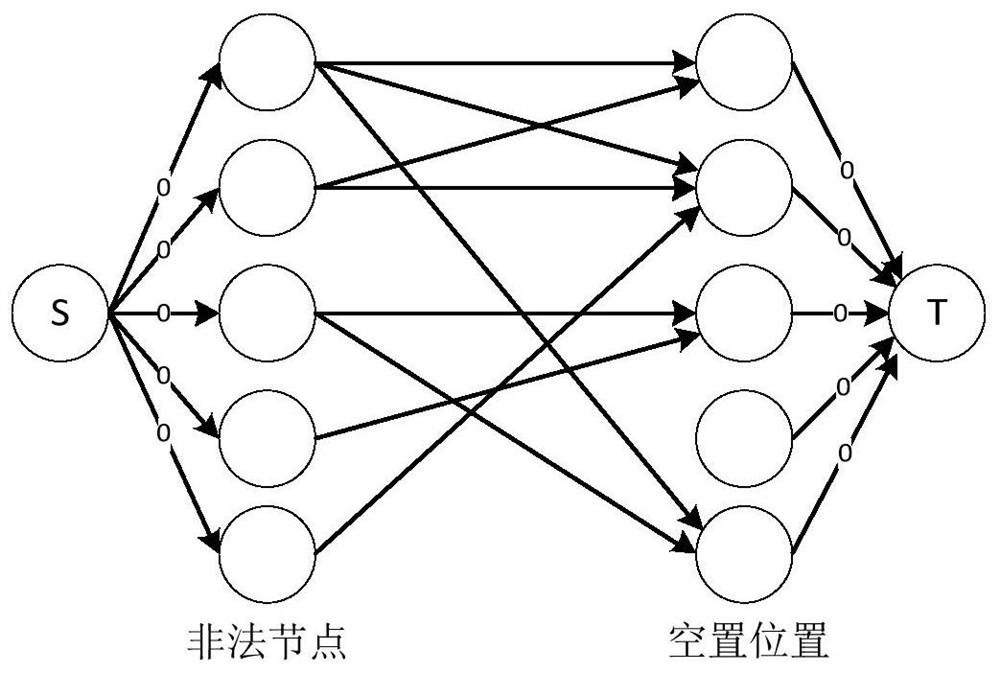

[0058] This application discloses a FPGA layout legalization method based on the maximum flow algorithm, please refer to figure 2 Shown in the flow chart, the method comprises the steps:

[0059] In step S1, after the initial layout of the FPGA is completed, the line lengths of each net are determined according to the initial layout state of the FPGA.

[0060] There are several layout positions on the FPGA. During the initial layout, each distributable unit in the layout netlist is placed on the FPGA using a layout algorithm. The layout algorithm used during the initial layout can be a conventional analytical algorithm, which is not described in this application. After the initial layout is completed, a part of the distributable units in the layout netlist will be designated to be arranged at each layout position of the FPGA, then the layo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com