Super-junction insulated gate bipolar transistor structure and manufacturing method thereof

A technology of bipolar transistors and super junctions, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of low conduction efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

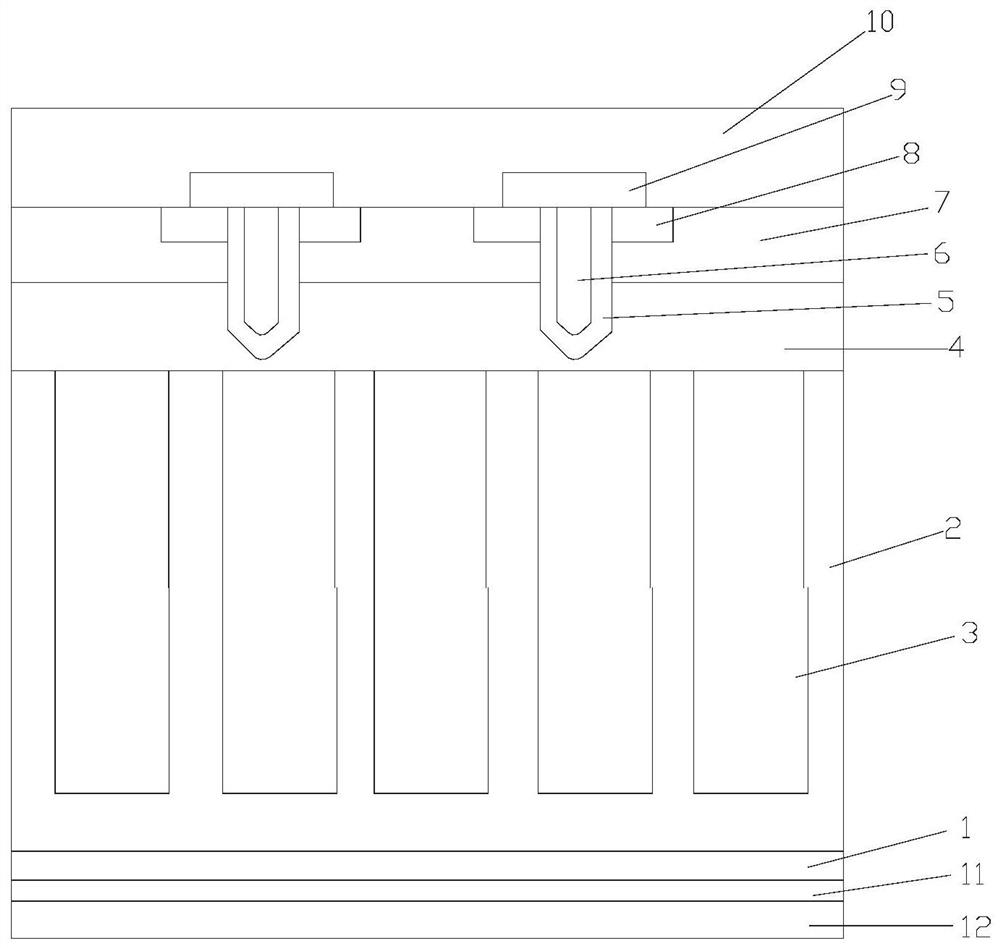

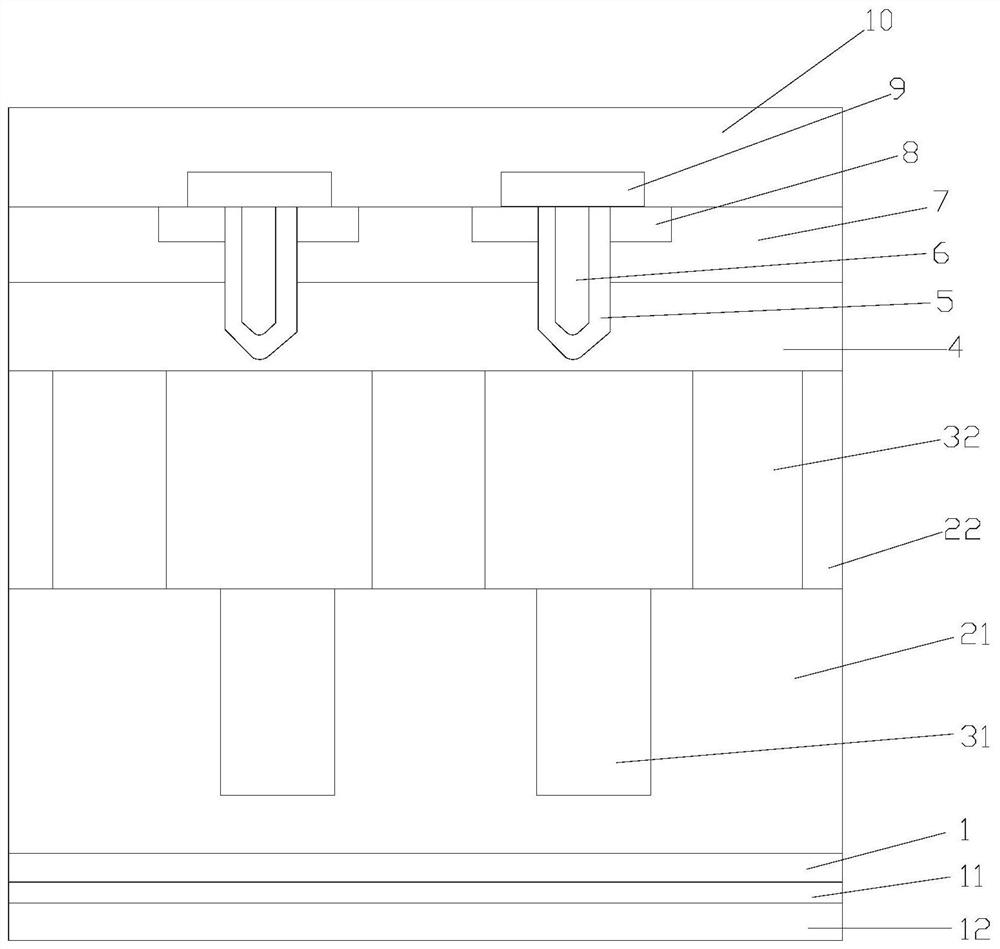

[0049] see figure 2 , a super junction insulated gate bipolar transistor structure, which includes a collector metal 12, a P+ collector 11, a P-collector region 1, a first N-drift region 21, a second N - drift region 22, N+ drift region 4, P well region 7 and emitter metal 10;

[0050] A plurality of first P-type super junctions 31 arranged at intervals are distributed in the first N-drift region 21, and a plurality of second P-type pillars 32 arranged at intervals are distributed in the second N-drift region 22, each A first P-type column 31 corresponds to at least one second P-type column 32 and forms a P-type super junction structure, and the first P-type column 31 and the second P-type column 32 are in the second direction Staggered from each other, the first P-type column 31 is also in contact with or connected to the second N-drift region 22, and the second P-type column 32 is also in contact with the first N-drift region 21 and the N+ drift region 4 respectively. or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com