CMOS protective layer structure and manufacturing method thereof

A manufacturing method and protective layer technology, applied in radiation control devices, electrical components, electrical solid devices, etc., can solve problems such as metal pollution and affecting device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

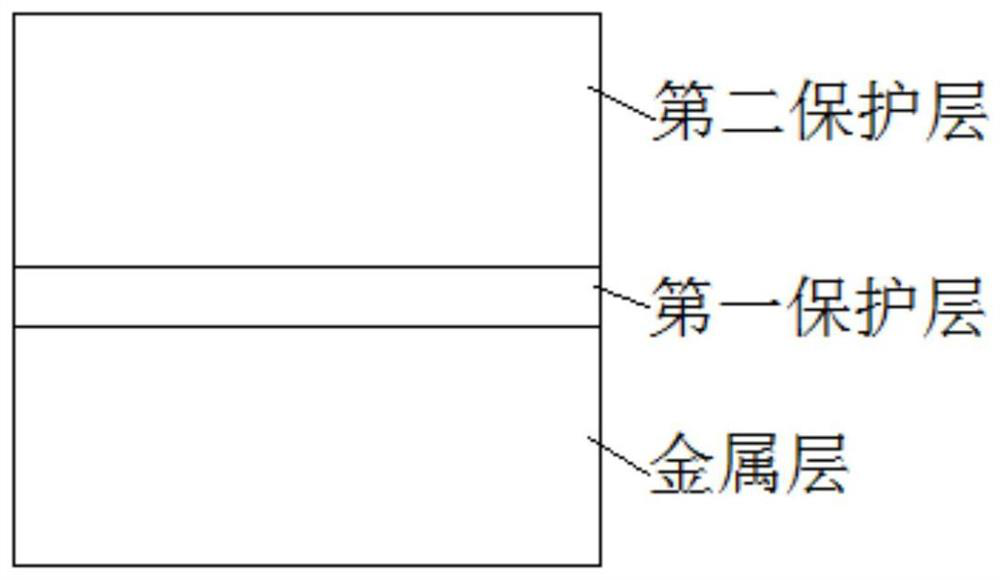

[0034] The first embodiment, such as figure 1 Said, the CMOS protection layer structure provided by the present invention, it is formed on the metal layer of CMOS, comprises:

[0035] a first protection layer deposited on the metal layer and having a thickness of a first thickness;

[0036] a second protection layer deposited on the first protection layer and having a thickness of a second thickness;

[0037] Wherein, the first protection layer and the second protection layer are nitride layers formed by depositing different materials, the second thickness is greater than the first thickness, and the temperature required for depositing the first protection layer is lower than the temperature required for depositing the second protection layer .

[0038] The first embodiment of the present invention can reduce the formation of bump defects well by reducing the metal precipitation degree. Therefore, depositing the first protective layer on the metal layer can effectively red...

no. 2 example

[0039] In the second embodiment, the CMOS protection layer structure provided by the present invention is formed on the metal layer of CMOS, including:

[0040] A carbon silicon compound layer is deposited and formed on the metal copper layer, and its thickness ranges from 100 angstroms to 150 angstroms;

[0041] A silicon nitride layer is deposited on the silicon nitride carbon compound layer, and its thickness ranges from 2000 angstroms to 3000 angstroms.

no. 3 example

[0042] In the third embodiment, the CMOS protection layer structure provided by the present invention is formed on the metal layer of CMOS, including:

[0043] A carbon silicon compound layer is deposited and formed on the metal copper layer with a thickness of 130 angstroms;

[0044] A silicon nitride layer is deposited on the silicon nitride layer to a thickness in the range of 2370 Angstroms.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com