A kind of vertical structure LED chip and preparation method thereof

A LED chip and vertical structure technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems affecting light output efficiency, current congestion, low light output efficiency of LED chips, etc., achieve high light output efficiency, reduce heat dissipation, and alleviate current congestion effect of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The directions shown in the accompanying drawings are up, down, left, and right. The raw materials used in each of the following examples are purchased directly.

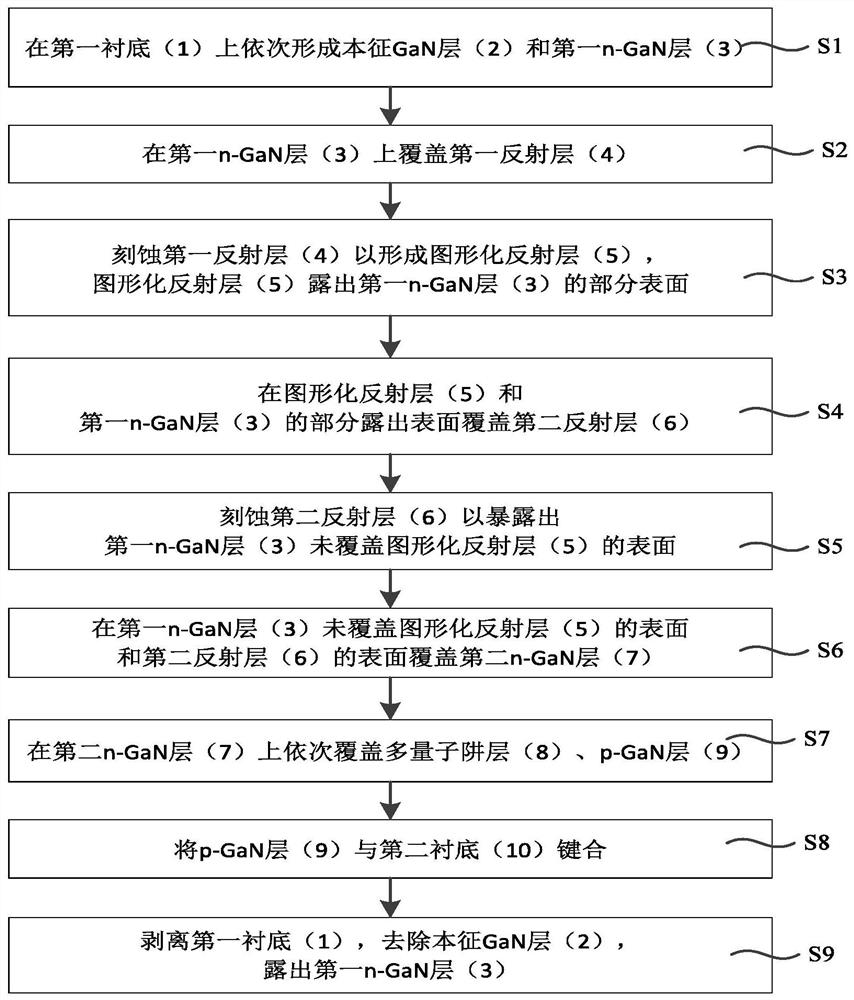

[0042] The preparation method of vertical structure LED chip is as follows figure 1 ,include:

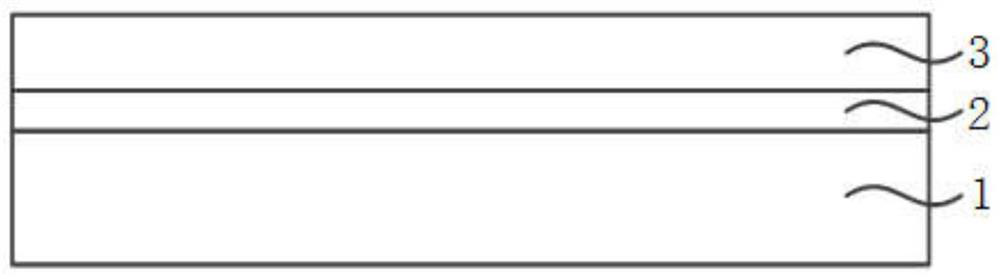

[0043] S1: providing a first substrate 1, and sequentially forming an intrinsic GaN layer 2 and a first n-GaN layer 3 on the first substrate 1;

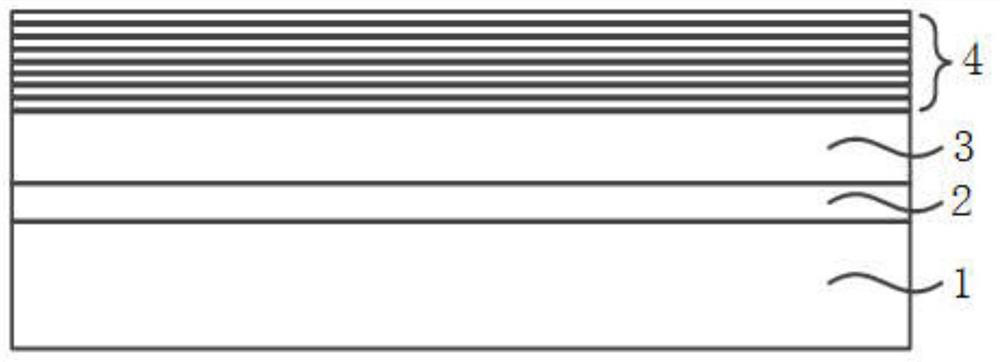

[0044] S2: forming the first reflective layer 4, the first reflective layer 4 covers the first n-GaN layer 3;

[0045] S3: Etching the first reflective layer 4 to form a patterned reflective layer 5, wherein the patterned reflective layer 5 exposes part of the surface of the first n-GaN layer 3;

[0046] S4: forming a second reflective layer 6, the second reflective layer 6 covers part of the surface of the patterned reflective layer 5 and the first n-GaN layer 3;

[0047] S5: etching the second reflective layer 6 to expose part of the surface of the first n-GaN layer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com