High-speed data caching structure and method

A high-speed data and data buffering technology, applied in the direction of electrical digital data processing, memory systems, instruments, etc., can solve the problems of increasing development difficulty and time cost, unfavorable control, complex DDR circuit signals, etc., to improve fault tolerance and stability Sexuality, efficiency improvement, simple and direct effect of address control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Below in conjunction with accompanying drawing and specific embodiment of description, the present invention is described in detail:

[0023] The present invention will be further described in detail below in conjunction with the accompanying drawings and examples. The following examples are explanations of the present invention and the present invention is not limited to the following examples.

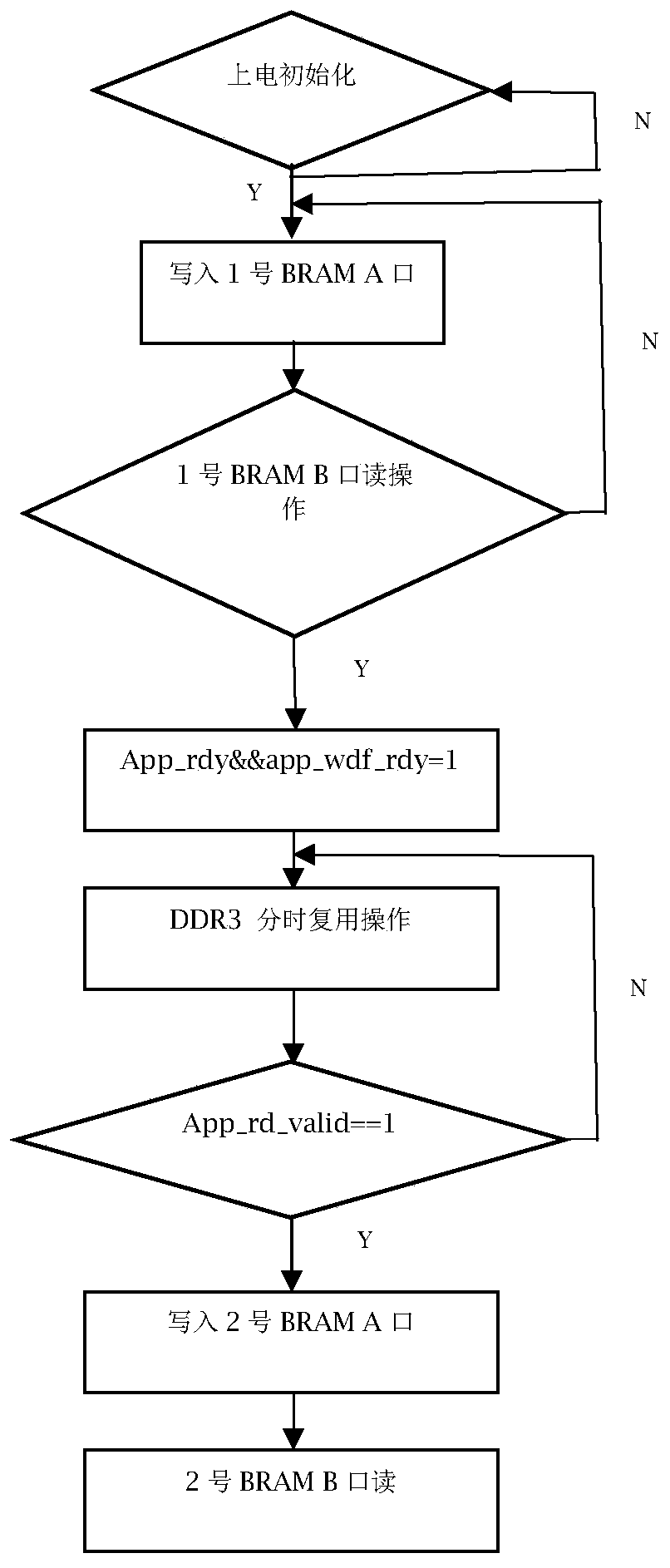

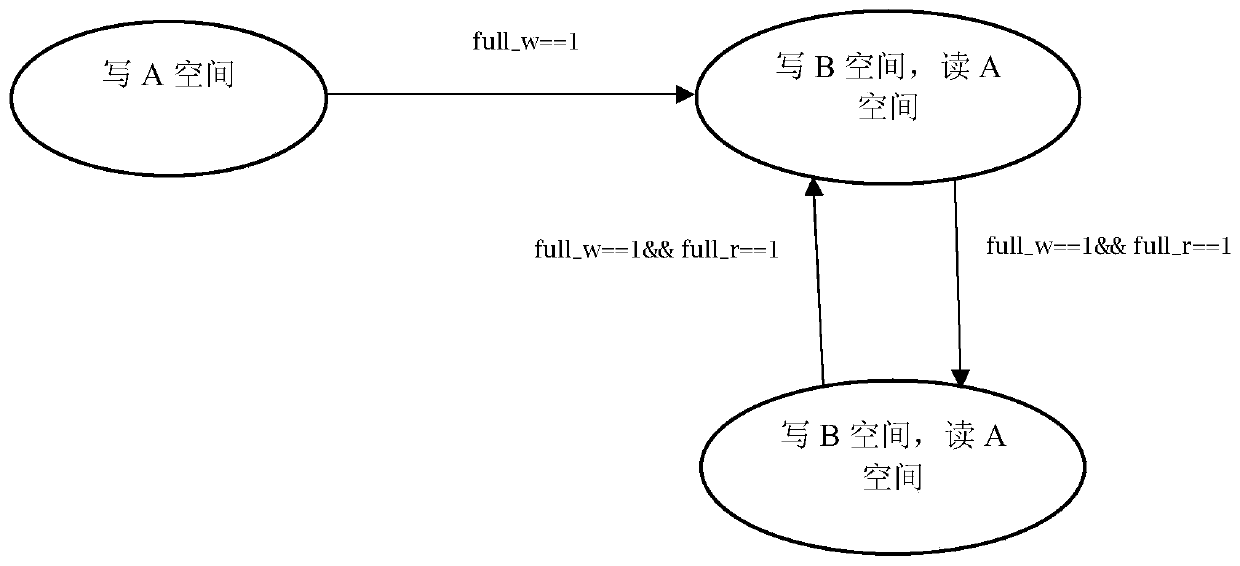

[0024] Such as figure 1 As shown, the present invention provides a high-speed data cache structure, which consists of four parts: a front-end receive data cache unit, a middle-end large-capacity data buffer unit, a back-end send data cache unit, and a cache data control unit. The front-end receiving data buffer unit is mainly composed of dual-port Block RAM. The A port of the BRAM of the front-end receiving data buffer unit writes the data to be buffered, and the B port reads out to the middle-end large-capacity data buffer unit. The mid-range large-capacity data cache unit i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com