Multi-stage FPGA wiring method for optimizing time division multiplexing technology

A technology of time-division multiplexing and wiring method, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problem of increased inter-chip signal delay, and achieve optimal inter-chip signal delay and optimal inter-chip signal delay. The effect of optimizing and solving routability problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

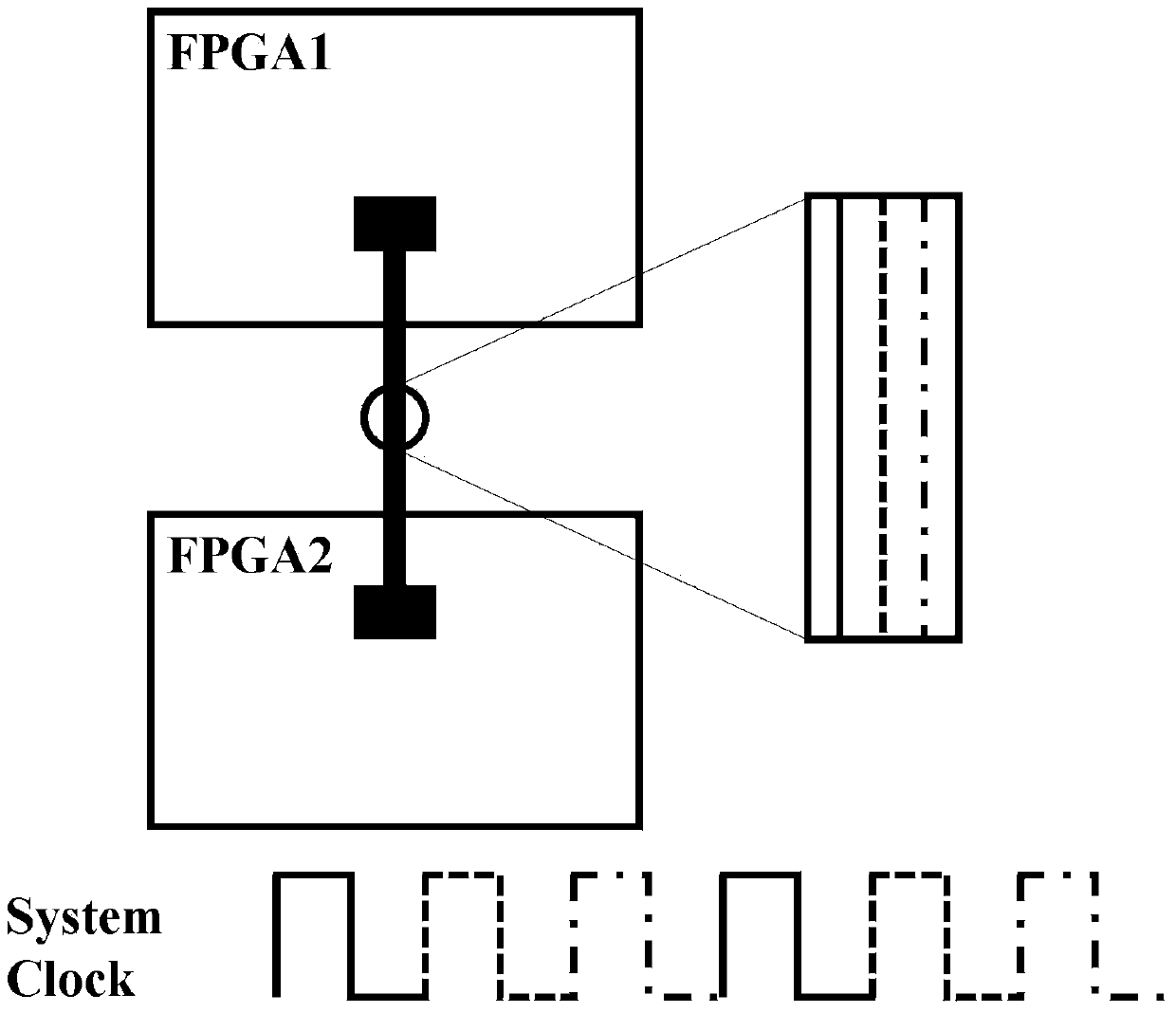

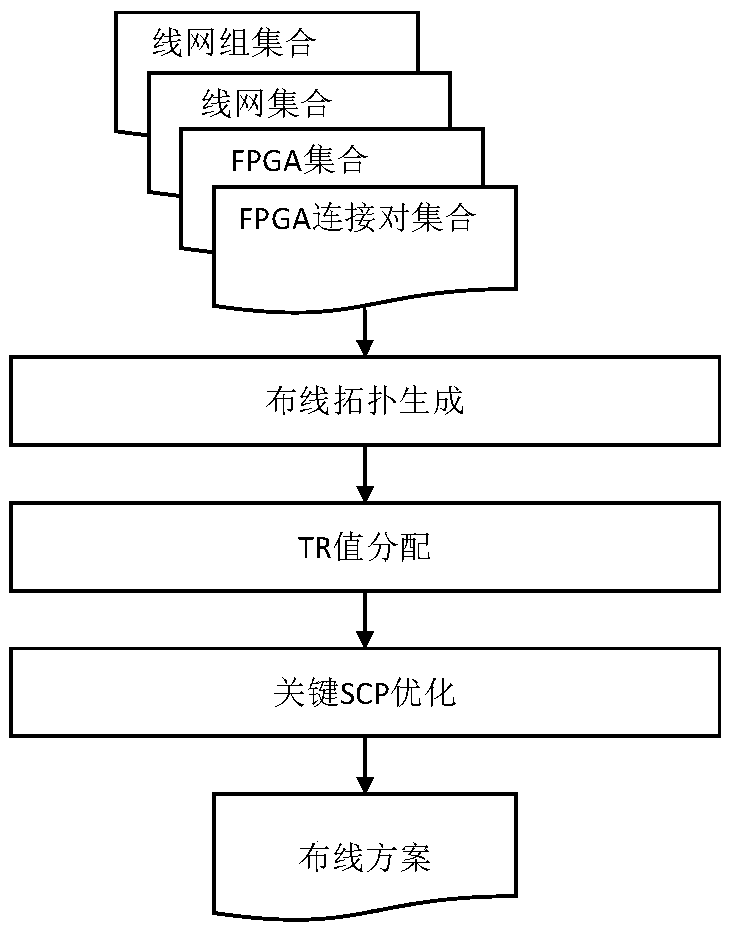

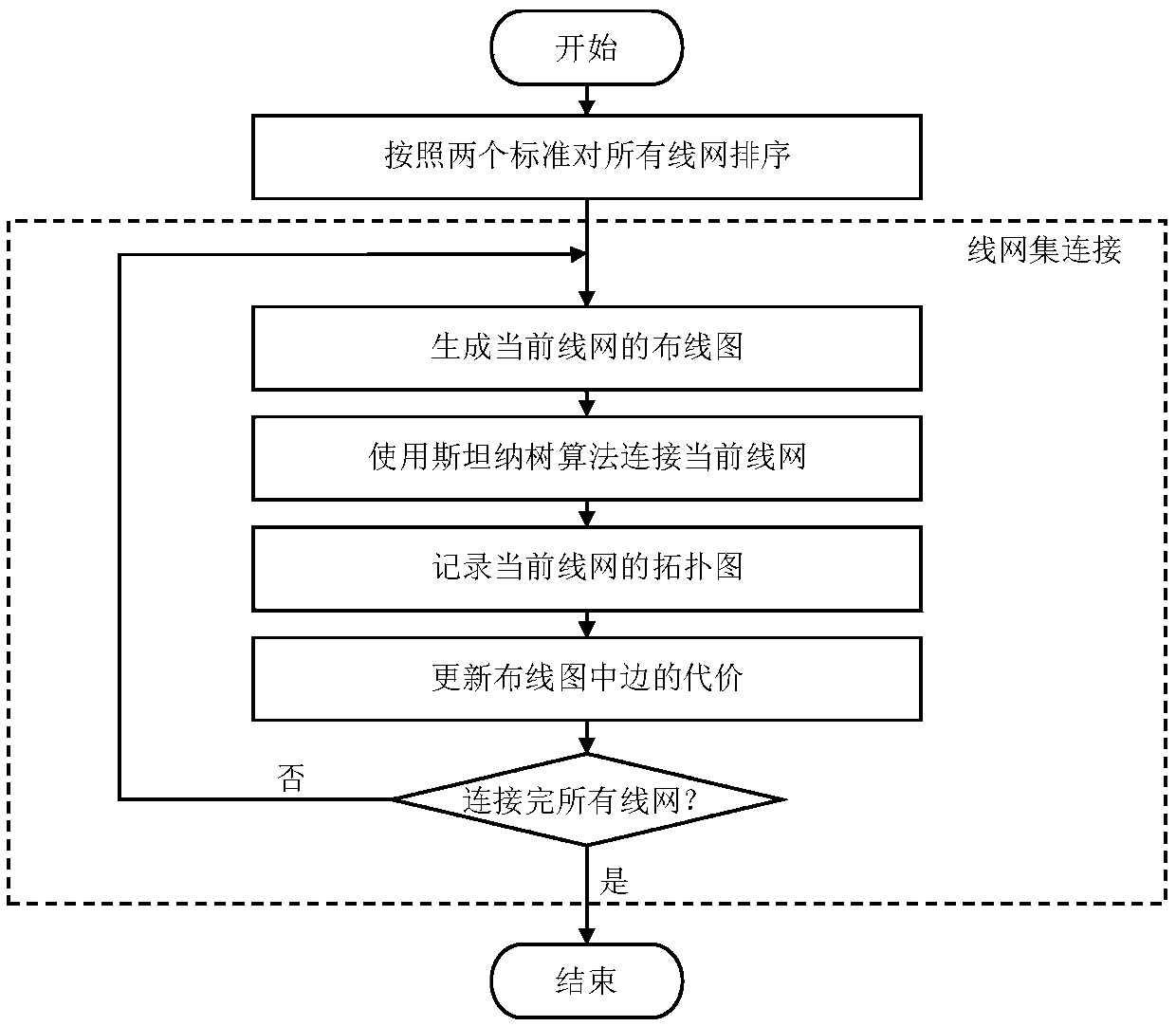

[0065] Please refer to figure 2 , the present invention provides a kind of multistage FPGA wiring method of optimization time division multiplexing technique, comprises the following steps:

[0066] Step S1: collect FPGA set, FPGA connection pair set, line net set and line net group set;

[0067] Step S2: according to the FPGA set, the FPGA connection pair set, the line net set and the line net group set, obtain the wiring topology of the line net without assigning TR;

[0068] Step S3: according to the difference of the delay situation of each wire net group, assign corresponding TR for each edge of each wire net;

[0069] Step S4: cyclically perform TR reduction and edge legalization, and iteratively optimize the net group whose TR value is greater than the preset value, until the iteration termination condition is satisfied, and an optimal wiring ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com