Design Method for Optimizing the Metal Routing of Fishbone Clock Tree

A technology of metal routing and design method, applied in computer-aided design, calculation, instrument, etc., can solve the problems of affecting clock quality, large backbone load, large clock conversion time delay, etc., to achieve good clock quality and small clock deviation. , the effect of reducing the length of the winding

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

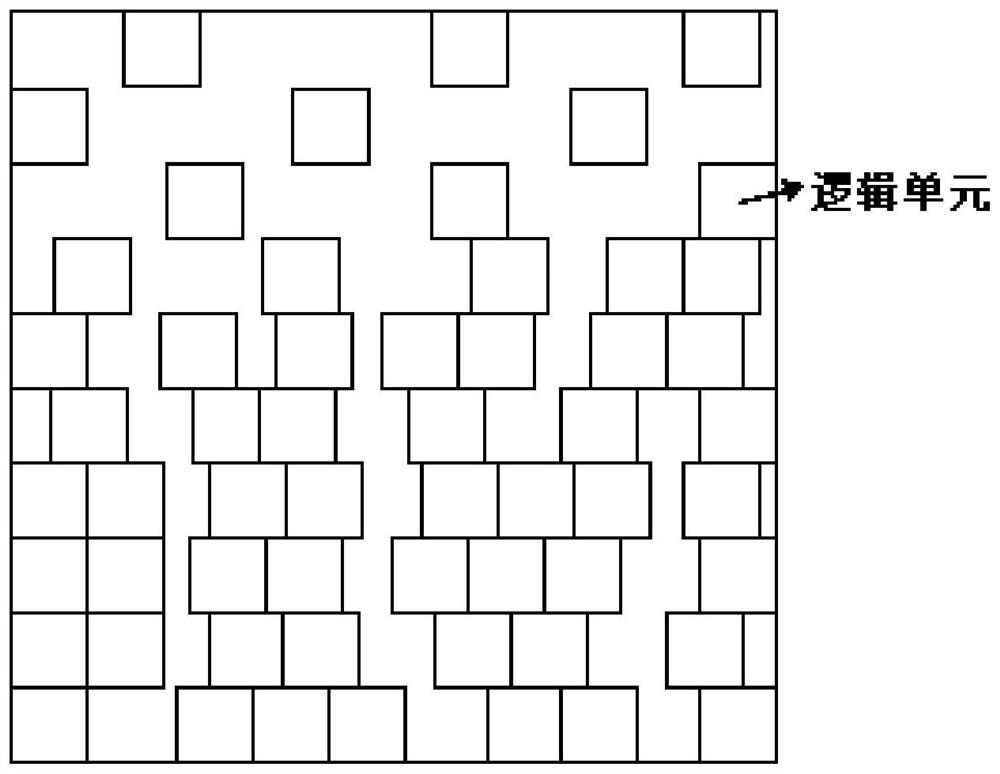

[0014] In the process of chip back-end design, tools automatically place and route, and logic units are usually placed in an unreasonable position and partially piled up. Blockage of metal traces, causing violation of design rules, leading to chip failure. figure 1 and figure 2 In contrast, the same number of logic units are placed in the same area, which is obviously visible. figure 2 compared to figure 1 The logical unit placement is more even and reasonable.

[0015] In the stage of placing logic units in traditional chip design, the density of logic units will be restricted in the overall area of the chip. However, since some logic units have many connections with each other, the tool will optimize according to the timing. In order to meet the timing requirements, as much as possible Put related logical units together. like figure 1 , the tool will place some logic units very closely, and others will be placed loosely if they have little connection with each other...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com