Method for generating multi-fan-out clock signal facing superconducting RSFQ circuit

A clock signal and circuit technology, applied in the field of clock tree topology optimization, can solve problems such as not considering the clock tree structure, and achieve the effects of low power consumption, small area, and small clock delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, and are not intended to limit the protection of the present invention. Any modifications, equivalent replacements and improvements made within the spirit and principle of the present invention shall be included in the protection scope of the claims of the present invention.

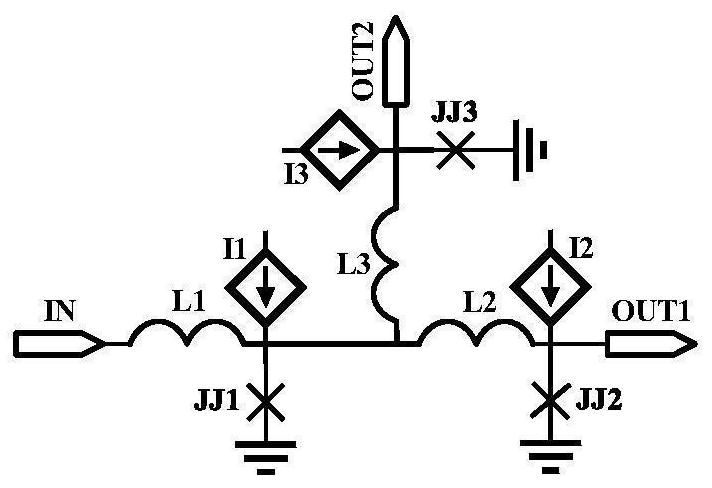

[0036] Figure 1A is the equivalent circuit of SPL2, as Figure 1A As shown, when a SFQ pulse is input to the input IN of SPL2, the same two outputs, OUT1 and OUT2, will be generated. Likewise, in SPL3 devices, when a SFQ pulse is fed to the input in SPL3, the same three outputs are generated.

[0037] Figure 1B It is the comparison of the fan-out of the CMOS ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com