Methods of manufacturing a vertical memory device

A memory and charge storage technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., and can solve problems such as the difficulty of semiconductor patterns

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] It should be noted that aspects of the inventive concept described in one embodiment may be incorporated into a different embodiment, although not specifically described in this regard. That is, all embodiments and / or features of any embodiment may be combined in any manner and / or combination. These and other objects and / or aspects of the inventive concept are described in detail in the following specification. As used herein, the term "and / or" includes any and all combinations of one or more of the associated listed items. Expressions such as "at least one of," when preceding a list of elements, modify the entire list of elements and do not modify the individual elements of the list.

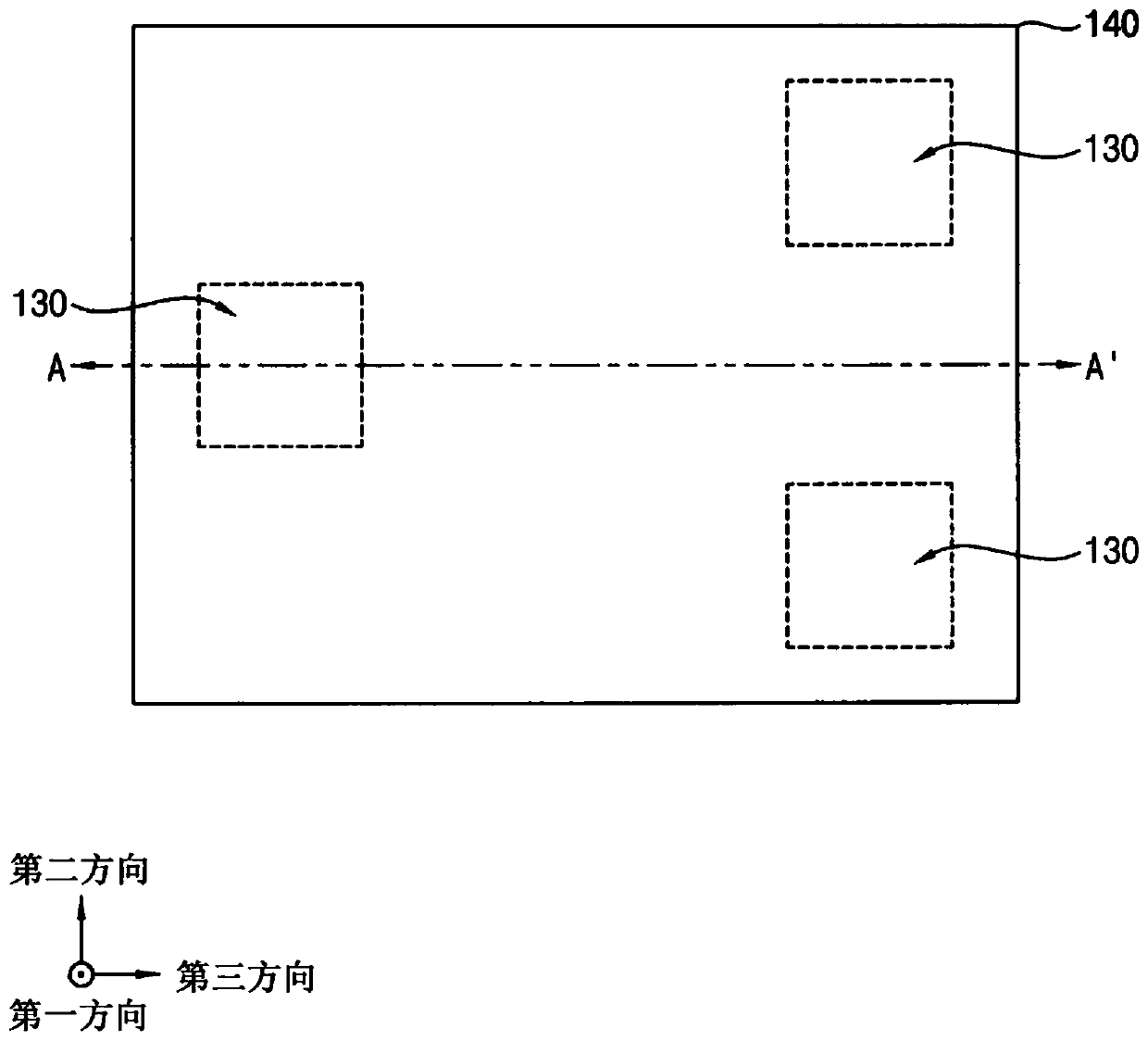

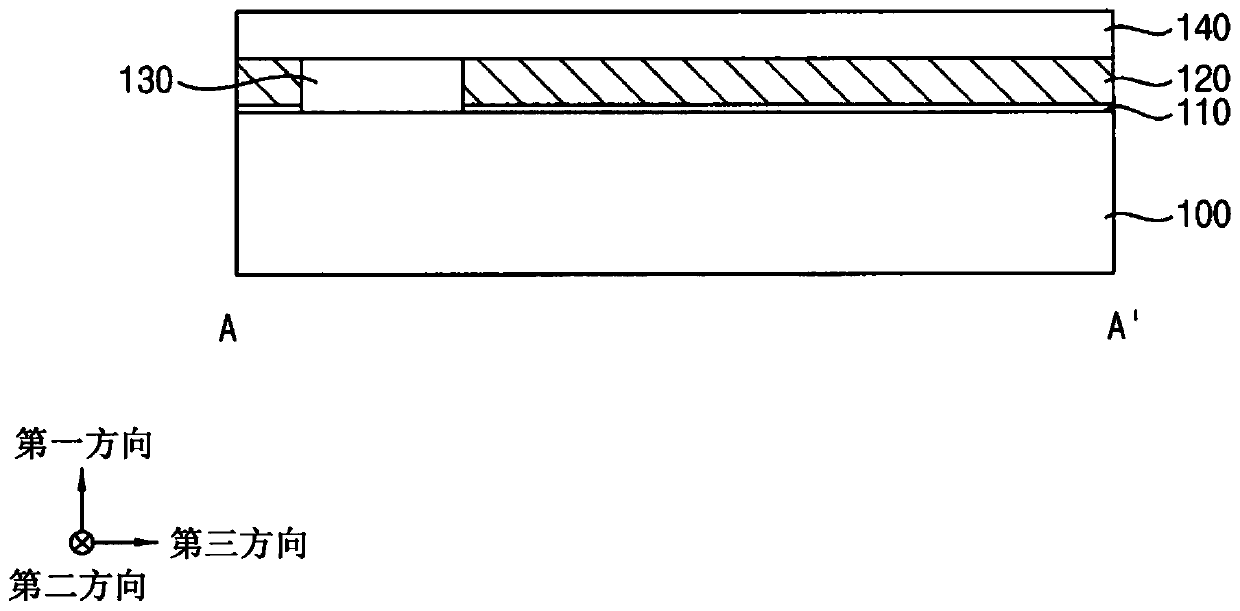

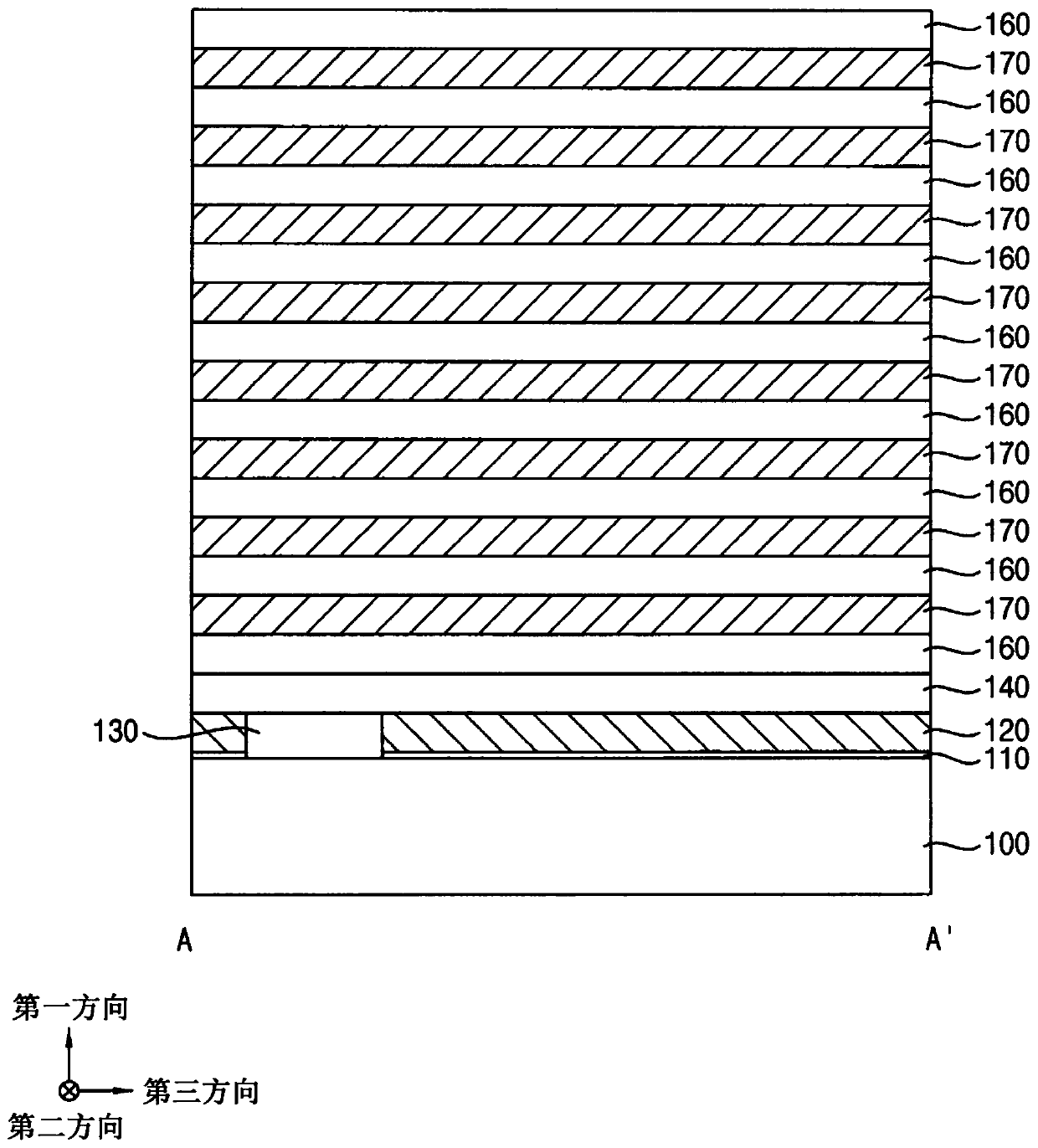

[0014] The above and other aspects and characteristics of a vertical memory device and a method of manufacturing the same according to example embodiments will become readily understood from the following detailed description with reference to the accompanying drawings. Hereinafter, a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com