A Realization Method of Vector Aggregate Load Instruction

An implementation method and instruction technology, which are applied in the implementation field of vector aggregated load instructions, can solve the duplication of the micro-operation management function of a vector buffer unit and the function of the launch queue, and cannot support multiple vector aggregated load instructions and multiple vector aggregated loads at the same time. Instructions cannot be executed in parallel, so as to reduce the number of micro-operations, reduce Perm operations, and improve program performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

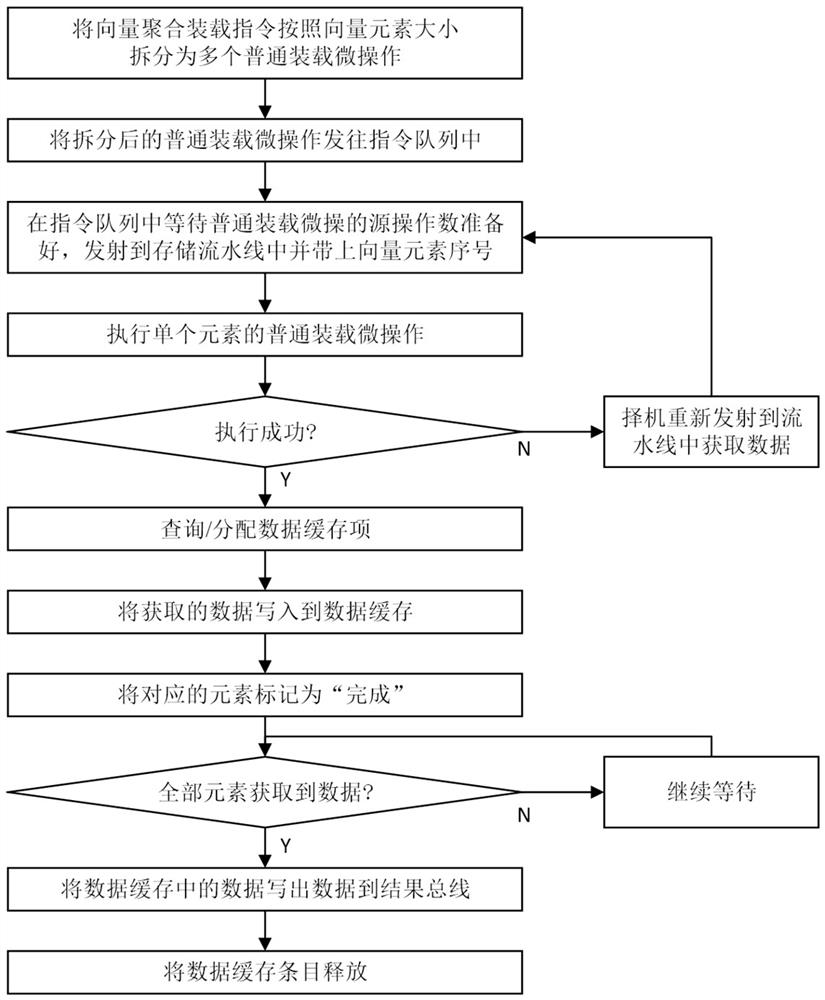

[0034] Such as image 3 As shown, the implementation steps of the implementation method of the vector aggregation load instruction in this embodiment include:

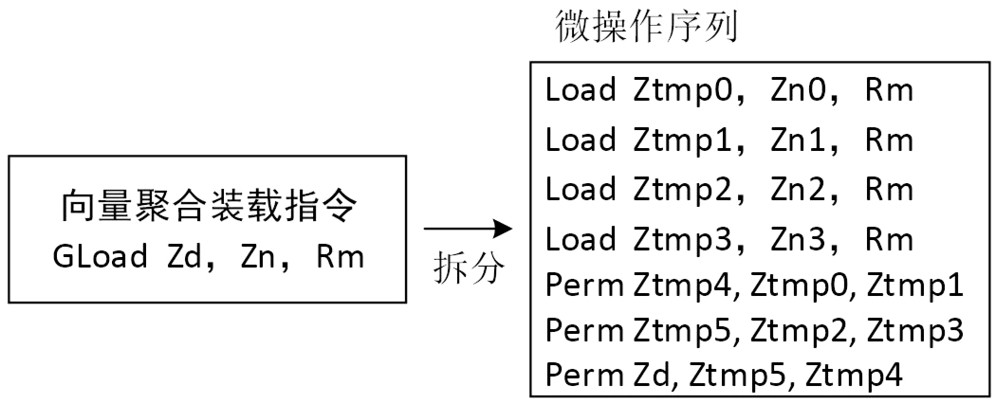

[0035] 1) Split the vector aggregate loading instruction into multiple common loading micro-operations according to the size of the vector elements;

[0036] 2) Send the split normal load micro-operation to the instruction queue;

[0037] 3) Waiting for the source operand of the common load micro-operation to be ready in the instruction queue, and launching the corresponding common load micro-operation to the storage pipeline after the source operand is ready and carrying the vector element number;

[0038] 4) Execute common loading micro-operations for a single element;

[0039] 5) Judging whether the execution is successful, if the execution is successful, jump to the next step; otherwise, the launch queue needs to choose an opportunity to re-transmit the memory access operation of the element to the pipeline to ob...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com