Preparation method of SOI wafer

A wafer and polysilicon technology, applied in the field of microelectronics, can solve the problems of difficult to produce materials with good thermal stability, low substrate surface resistivity, difficult to control, etc., so as to reduce the loss of the radio frequency substrate and reduce the parasitic surface. Conductivity, loss reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

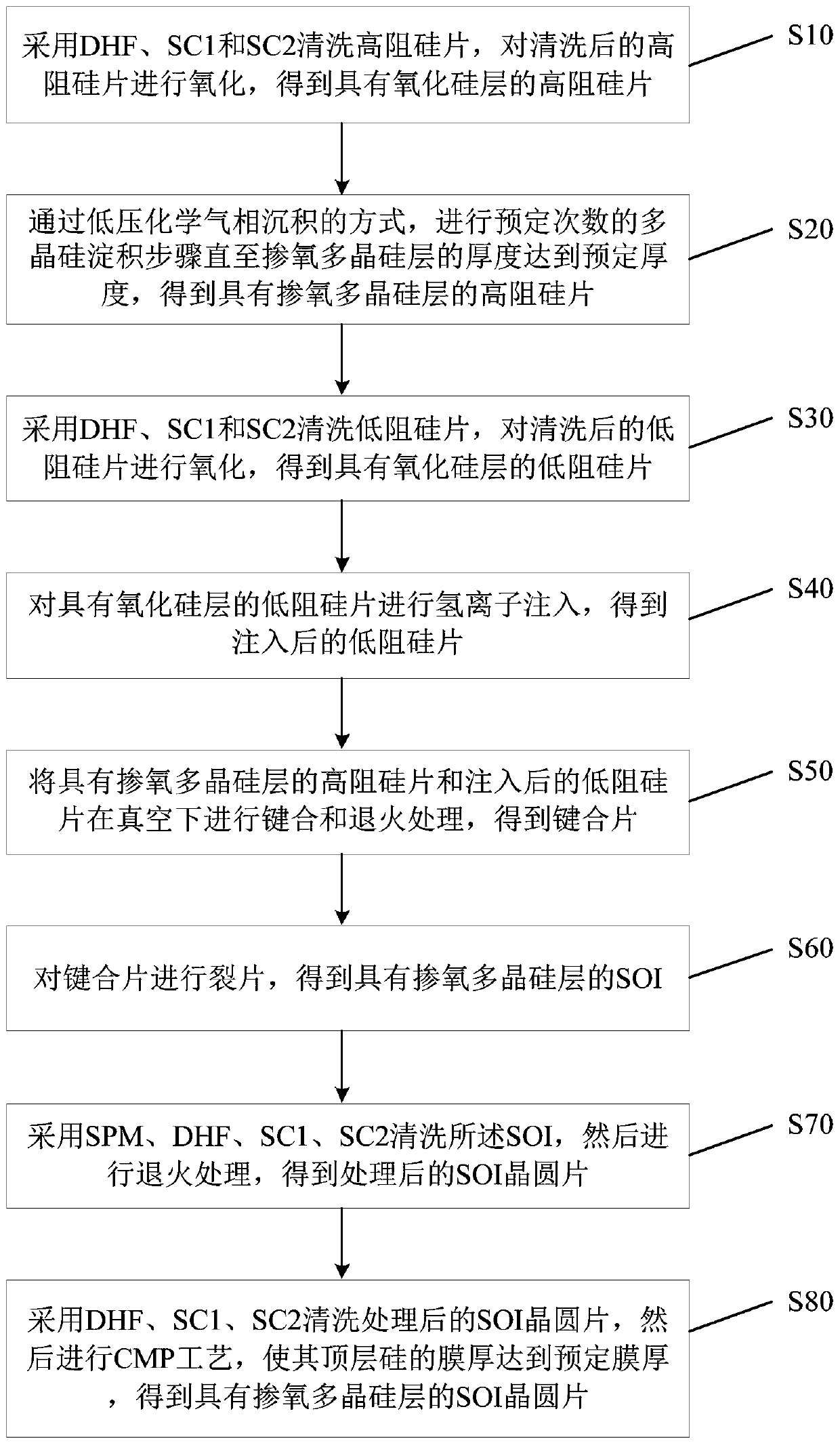

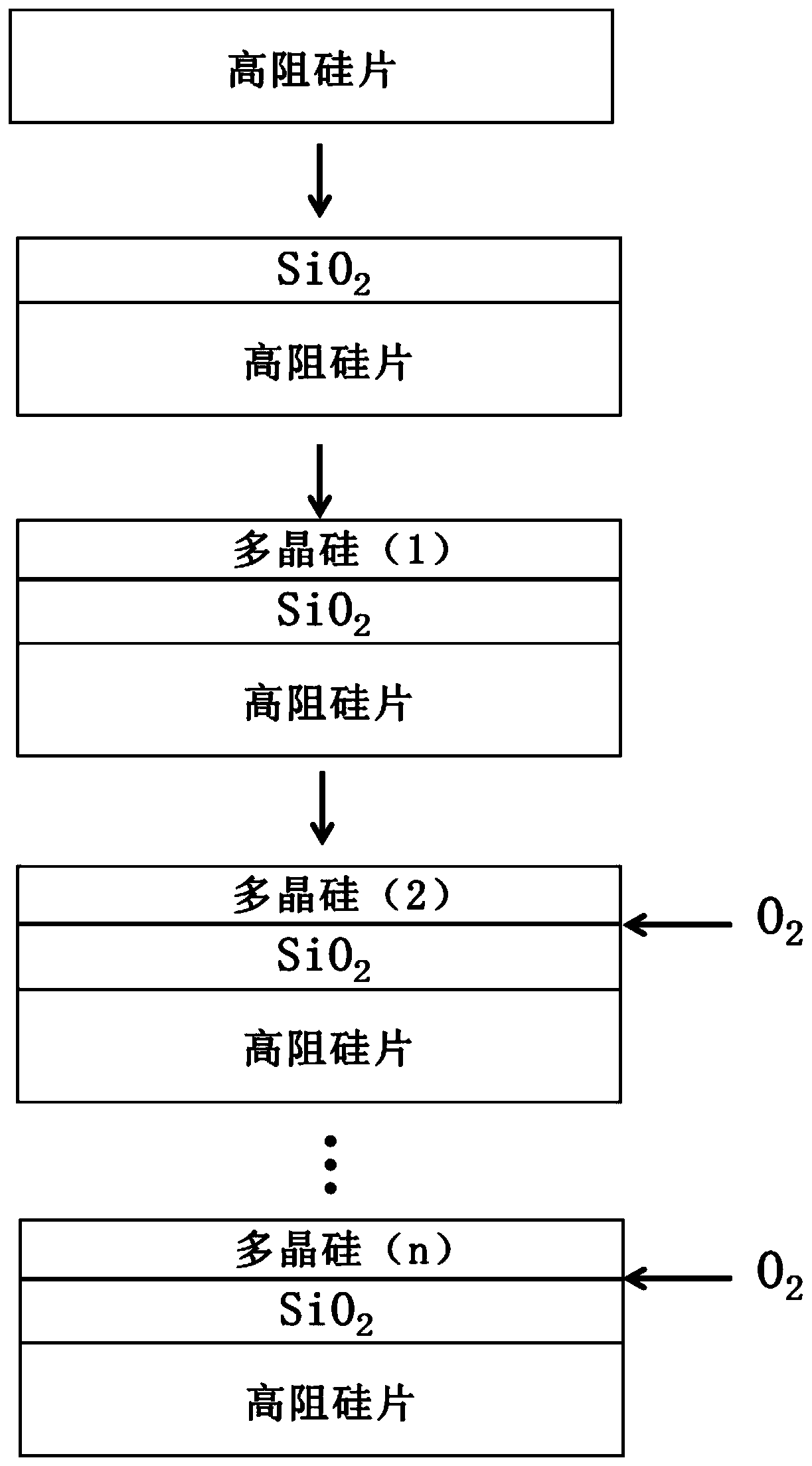

[0020] refer to Figure 1 to Figure 4 , in step S10, adopt DHF (hydrofluoric acid), SC1 and SC2 to clean the high-resistance silicon chip successively, the high-resistance silicon chip after cleaning is oxidized, obtain the silicon oxide layer (for example silicon dioxide SiO 2 ) high-resistance silicon wafer.

[0021] As an example, DHF, SC1 and SC2 are used to clean the high-resistance silicon wafer in sequence for 1-2 hours each, so as to remove the natural oxide layer and pollutants on the surface of the high-resistance silicon wafer. Specifically, DHF is used to remove the natural oxide layer; SC1 is a mixed solution of ammonia, hydrogen peroxide and ultrapure water for removing surface particles; SC2 is a mixed solution of hydrochloric acid, hydrogen peroxide and ultrapure water for cleaning metal contamination.

[0022] Preferably, the cleaned high-resistance silicon wafer is placed in an oxidation furnace with an oxidation temperature of 1100° C., and a silicon oxide ...

Embodiment 2

[0056] This embodiment provides a method for preparing an SOI wafer, including:

[0057] Use DHF, SC1 and SC2 to clean the high-resistance silicon wafer in sequence, and oxidize the cleaned high-resistance silicon wafer at a temperature of 1150° C. to obtain a high-resistance silicon wafer with a silicon oxide layer. The thickness of the silicon oxide layer is

[0058] By means of low-pressure chemical vapor deposition, under the conditions of growth pressure 3.5 Torr and reaction temperature 610°C, two polysilicon deposition steps are carried out until the thickness of the oxygen-doped polysilicon layer reaches 1.2 μm, and high-resistance silicon with an oxygen-doped polysilicon layer is obtained. sheet; wherein, the polysilicon deposition step is: deposit polysilicon on the surface of the silicon oxide layer, and then pass through 0.8% oxygen / argon for 3 minutes;

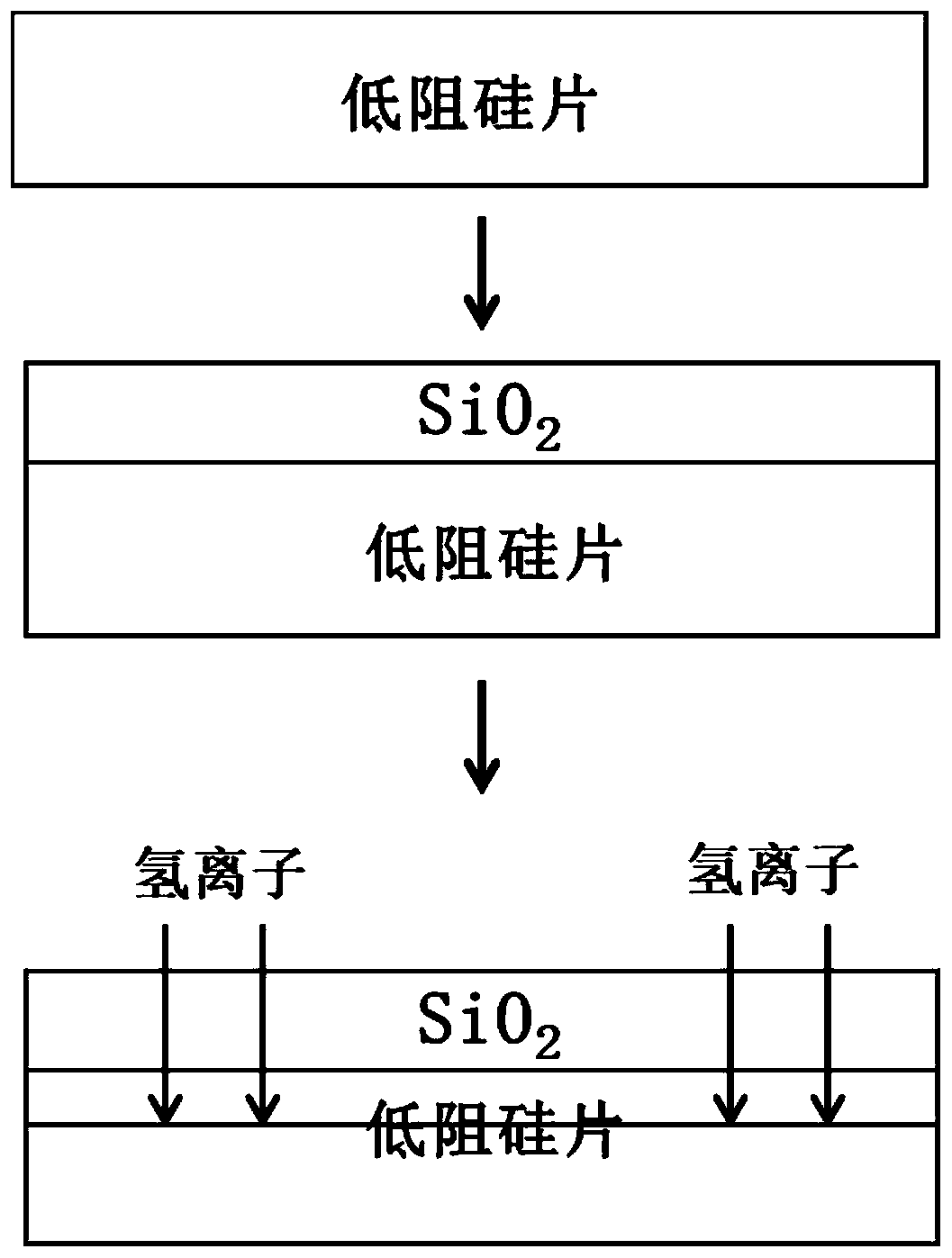

[0059] Use DHF, SC1 and SC2 to clean the low-resistance silicon wafer in sequence, and oxidize the cleaned lo...

Embodiment 3

[0067] This embodiment provides a method for preparing an SOI wafer, including:

[0068] Use DHF, SC1 and SC2 to clean the high-resistance silicon wafer in sequence, and oxidize the cleaned high-resistance silicon wafer at a temperature of 1100° C. to obtain a high-resistance silicon wafer with a silicon oxide layer. The thickness of the silicon oxide layer is

[0069] By means of low-pressure chemical vapor deposition, under the conditions of growth pressure 0.5 Torr and reaction temperature 650°C, four polysilicon deposition steps are carried out until the thickness of the oxygen-doped polysilicon layer reaches 1.8 μm, and high-resistance silicon with an oxygen-doped polysilicon layer is obtained. sheet; wherein, the polysilicon deposition step is: depositing polysilicon on the surface of the silicon oxide layer, and then feeding 0.6% oxygen / argon gas for 4 minutes;

[0070] Use DHF, SC1 and SC2 to clean the low-resistance silicon wafer in sequence, and oxidize the cleaned...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Film thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com