Semiconductor memory structure and manufacturing method of bit line contact part thereof

A manufacturing method and contact technology, which are applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electric solid-state devices, etc., can solve the problems of increased bit line contact resistance, short circuit of bit lines, etc., and achieve the prevention of resistance increase, The effect of avoiding short circuit of the bit line and increasing the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

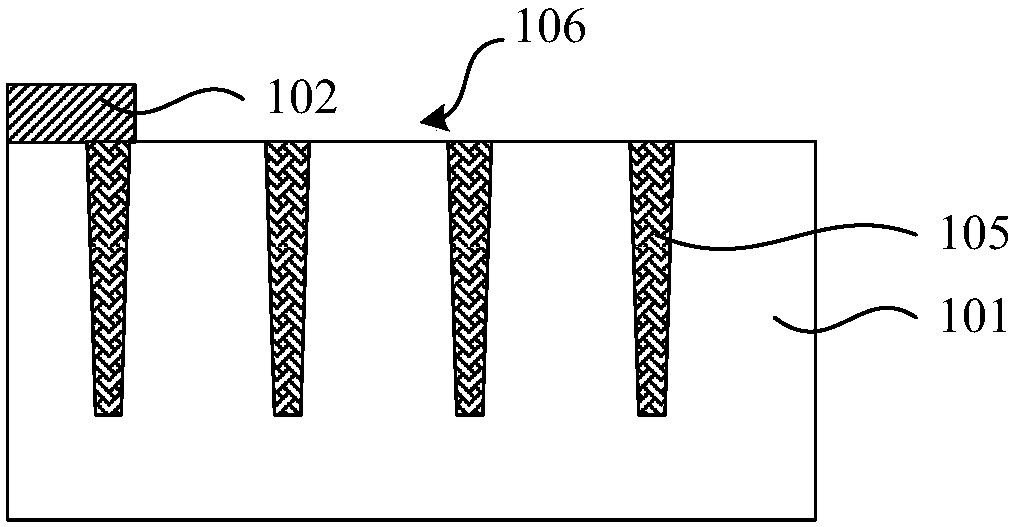

[0097] The present invention provides a method for manufacturing a bit line contact portion, comprising the following steps:

[0098] Such as Figure 10 As shown, step S1 is performed: providing a substrate 201 on which an etch stop layer 202 is formed.

[0099] Specifically, the substrate 201 may use conventional semiconductor materials such as Si, SiGe, SOI, etc. In this embodiment, the substrate 201 takes a silicon substrate as an example.

[0100] Specifically, an isolation structure 203 is further formed in the substrate 201 , and the isolation structure 203 defines a plurality of active regions 214 in the substrate 201 . In this embodiment, the isolation structure 203 is a shallow trench isolation structure (STI). According to the requirements of different semiconductor storage structures, the active region can adopt different layouts, and the protection scope of the present invention should not be excessively limited here.

[0101] Specifically, the etching stop laye...

Embodiment 2

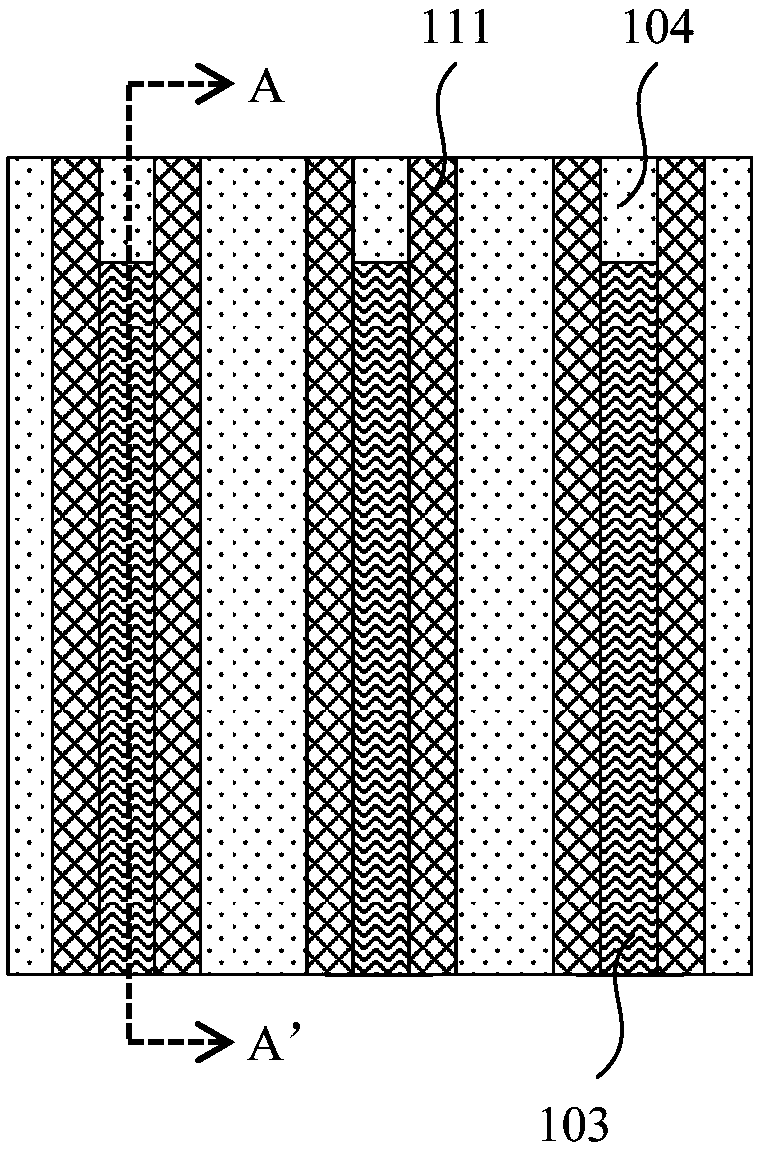

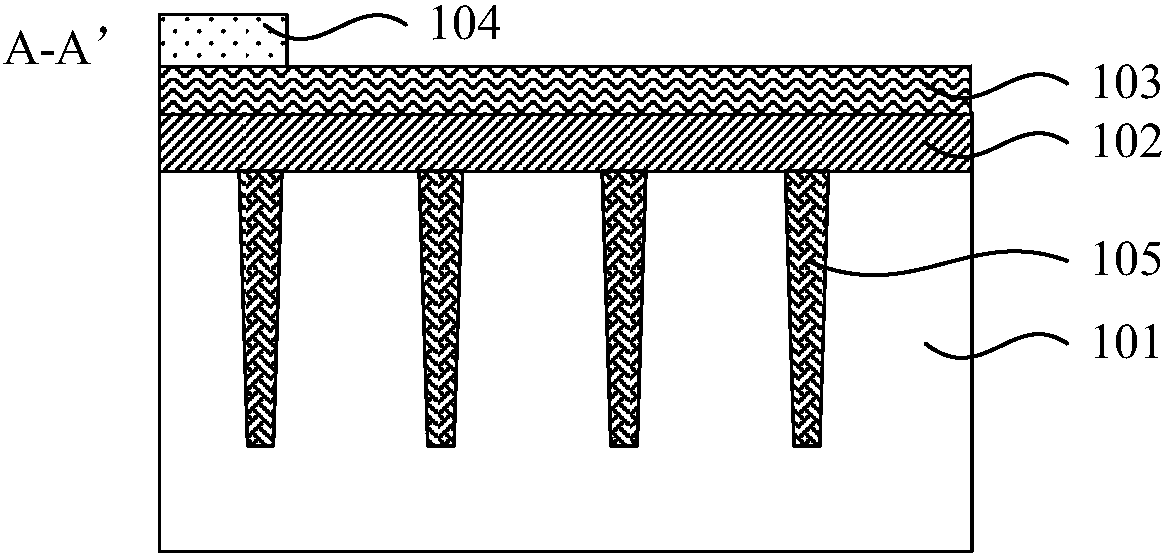

[0125] Such as Figure 20 and Figure 21 As shown, the present invention also provides a semiconductor memory structure, wherein, Figure 20 is shown as a top view of the semiconductor memory structure, Figure 21 shown as Figure 20 II' cross-sectional view of the shown structure, it can be seen that the semiconductor storage structure includes a substrate 201, a plurality of bit line contact isolation parts 205 of an etch stop layer, and a plurality of bit line contact parts 212 of a contact material and a plurality of bit lines 211 .

[0126] Specifically, a plurality of bit line contact isolation parts 205 are discretely arranged on the substrate 201 to isolate a plurality of bit line contact regions 215 in the substrate. In an extending direction, the substrate The upper surface of the bit line contact region and the top and side surfaces of the bit line contact isolation part form a contact material forming surface with a height difference.

[0127] Specifically, a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com