Elastic packaging structure for semiconductor chip

A packaging structure and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of high packaging cost, short service life, poor environmental adaptability, etc., to improve yield and reduce packaging The effect of high cost and high voltage level

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The present invention will be described in further detail below in conjunction with the accompanying drawings.

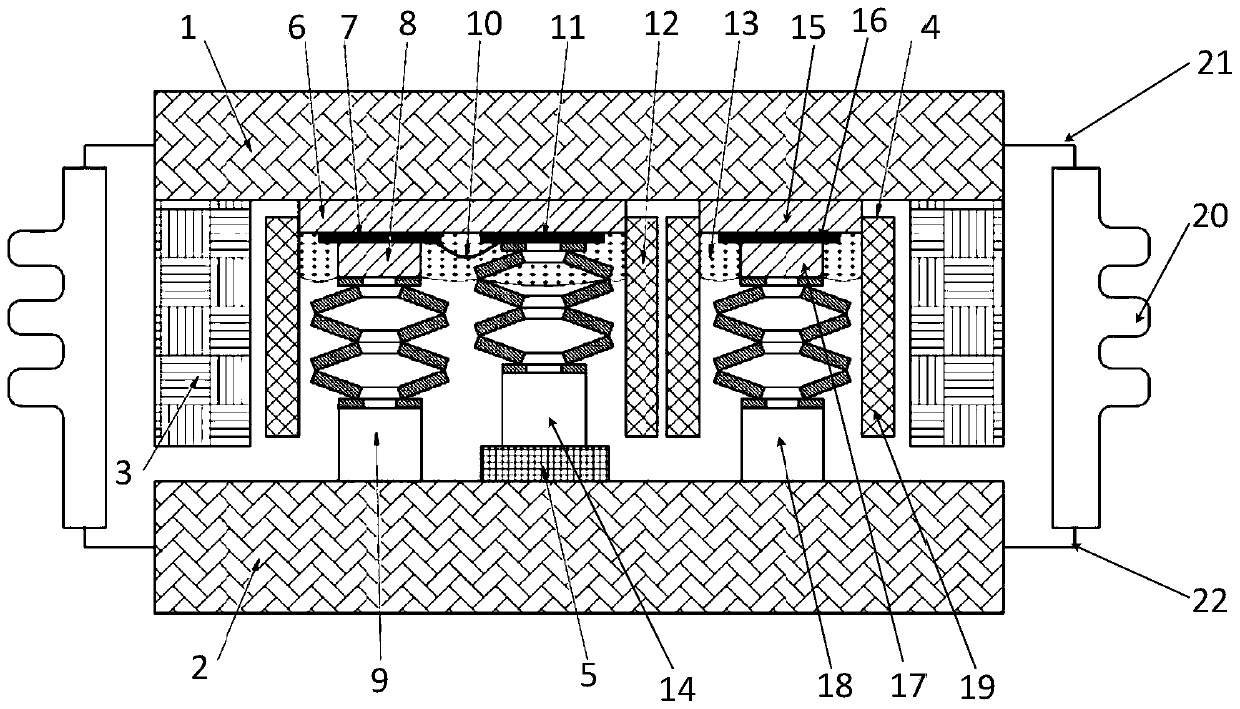

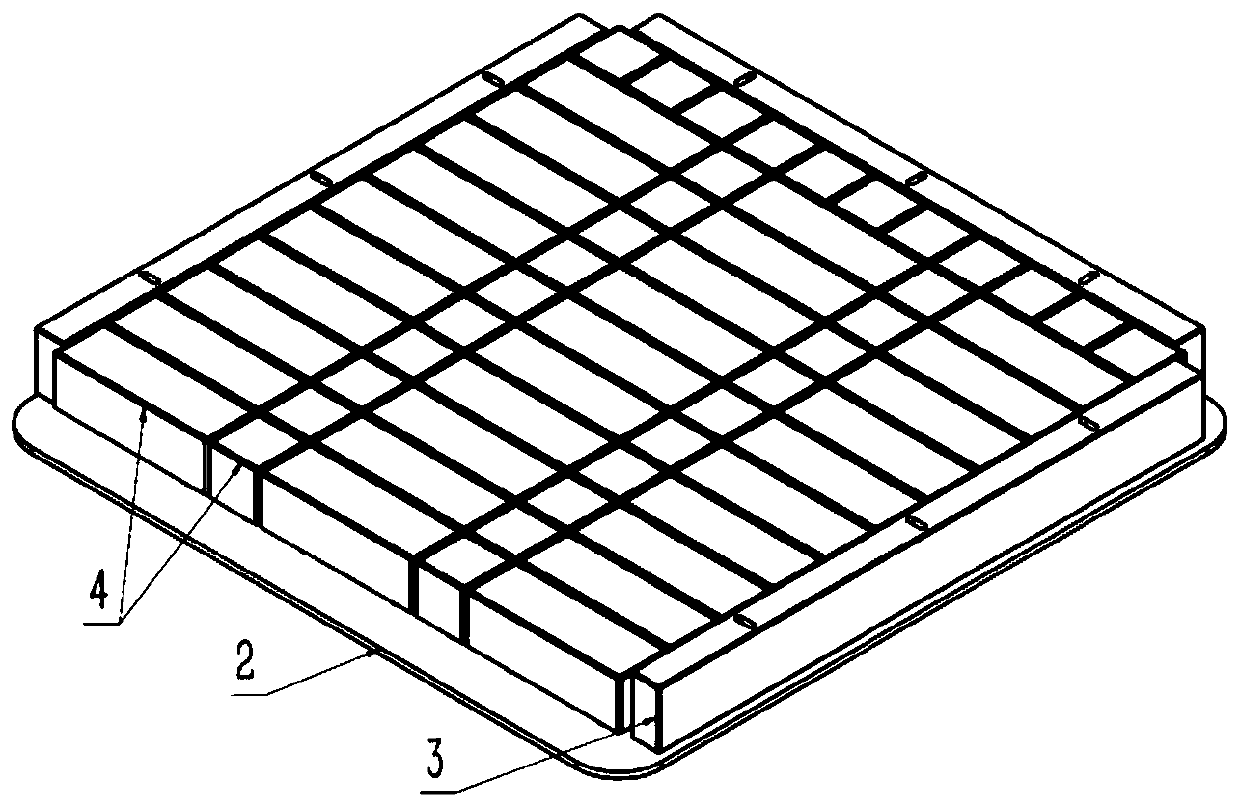

[0048] An embodiment of the present invention provides an elastic packaging structure for a semiconductor chip, such asfigure 1 As shown, it includes an upper electrode 1, a lower electrode 2, an annular packaging structure 20 and a plurality of chip subunits 4;

[0049] A plurality of chip sub-units 4 are arranged between the upper electrode 1 and the lower electrode 2; the annular packaging structure 20 is sealed and arranged on the sides of the upper electrode 1 and the lower electrode 2 and forms a closed shell structure with the upper electrode 1 and the lower electrode 2.

[0050] The elastic packaging structure provided by the embodiment of the present invention also includes an upper flange 21 and a lower flange 22;

[0051] The upper electrode 1 is welded to the annular packaging structure 20 through the upper flange 21 , and the lower electrode 2 is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com