Super-junction VDMOS device

A device and conductivity type technology, applied in the field of super-junction VDMOS devices, can solve the problems of super-junction MOSFET radiation effect and reinforcement research, VDMOS burnout, avalanche multiplication, etc., so as to reduce the probability of SEB, slow down the accumulation rate, The effect of reducing the current intensity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

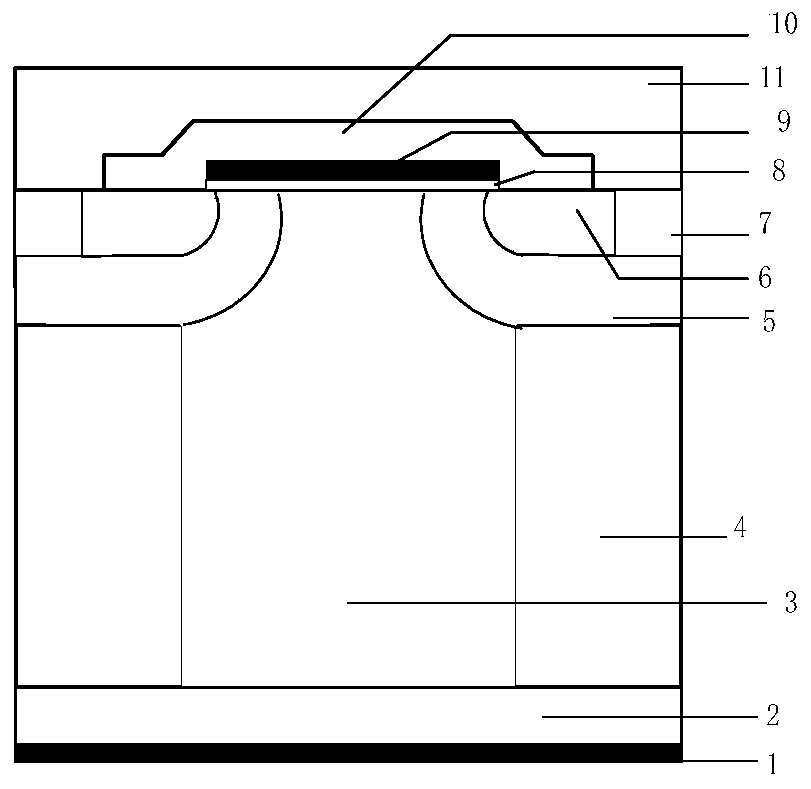

[0020]A super junction VDMOS device, comprising a first conductivity type heavily doped semiconductor substrate 2, a metallized drain electrode 1 located on the back of the first conductivity type heavily doped semiconductor substrate 2, a metallized drain electrode 1 located on the first conductivity type heavily doped semiconductor substrate The first conductivity type semiconductor column region 3 and the second conductivity type semiconductor column region 4 on the front surface of the substrate 2, the first conductivity type semiconductor column region 3 and the second conductivity type semiconductor column region 4 are arranged alternately, the second conductivity type semiconductor column region The top of 4 has a second conductivity type semiconductor base region 5, the side of the second conductivity type semiconductor base region 5 is in direct contact with the first conductivity type semiconductor column region 3, and the second conductivity type semiconductor base re...

Embodiment 2

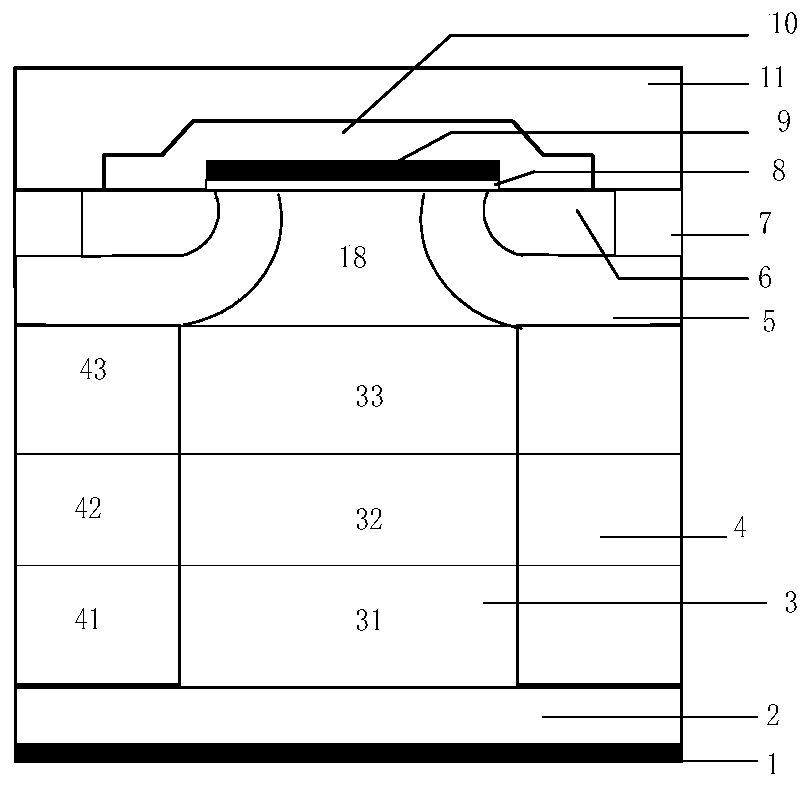

[0030] The difference between this embodiment and Embodiment 1 is: the first doped region 31 of the first conductivity type, the second doped region 32 of the first conductivity type, and the third doped region 33 of the first conductivity type. The impurity is non-uniformly distributed in this region, and the closer to the metallized drain side, the lower the doping concentration.

Embodiment 3

[0032] The difference between this embodiment and Embodiment 1 is: the first doped region 41 of the second conductivity type, the second doped region 42 of the second conductivity type, and the third doped region 43 of the second conductivity type. The impurity is non-uniformly distributed in this region, and the closer to the metallized drain side, the lower the doping concentration.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com