Chip package module and circuit board structure comprising the same

A chip packaging and circuit board technology, applied in the direction of circuit, printed circuit, printed circuit manufacturing, etc., to achieve the effect of volume reduction, high conductivity, and volume reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The foregoing and other technical contents related to the embodiments of the present invention will be clearly presented in the following detailed description of the embodiments with reference to the accompanying drawings. The directional terms mentioned in the following embodiments, such as "upper", "lower", "front", "rear", "left", "right", etc., are only referring to the directions of the accompanying drawings. Accordingly, the directional terms used are illustrative, not limiting, of the invention. Also, in the following embodiments, the same or similar components will be given the same or similar symbols.

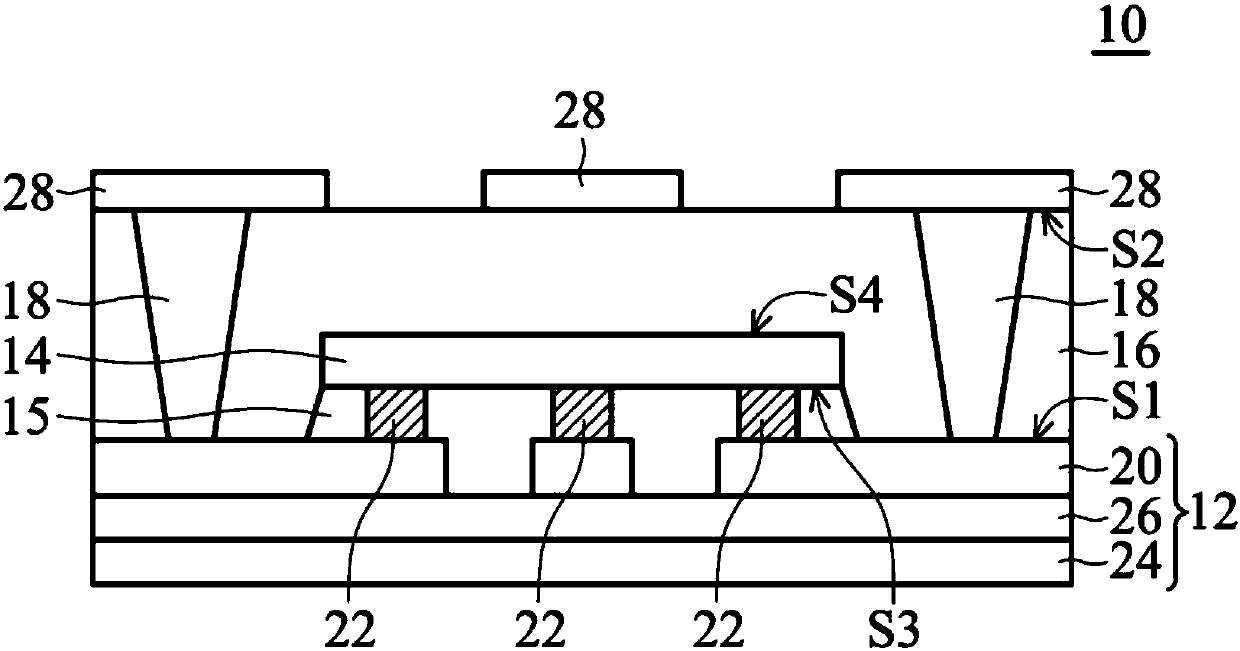

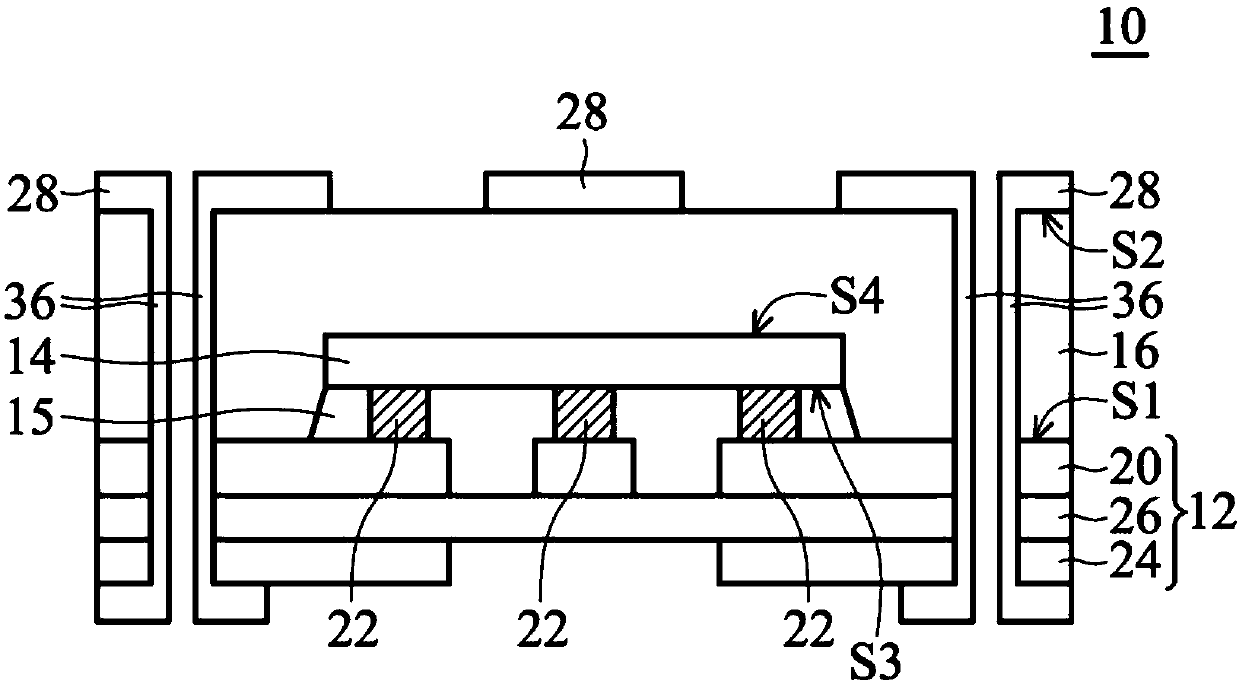

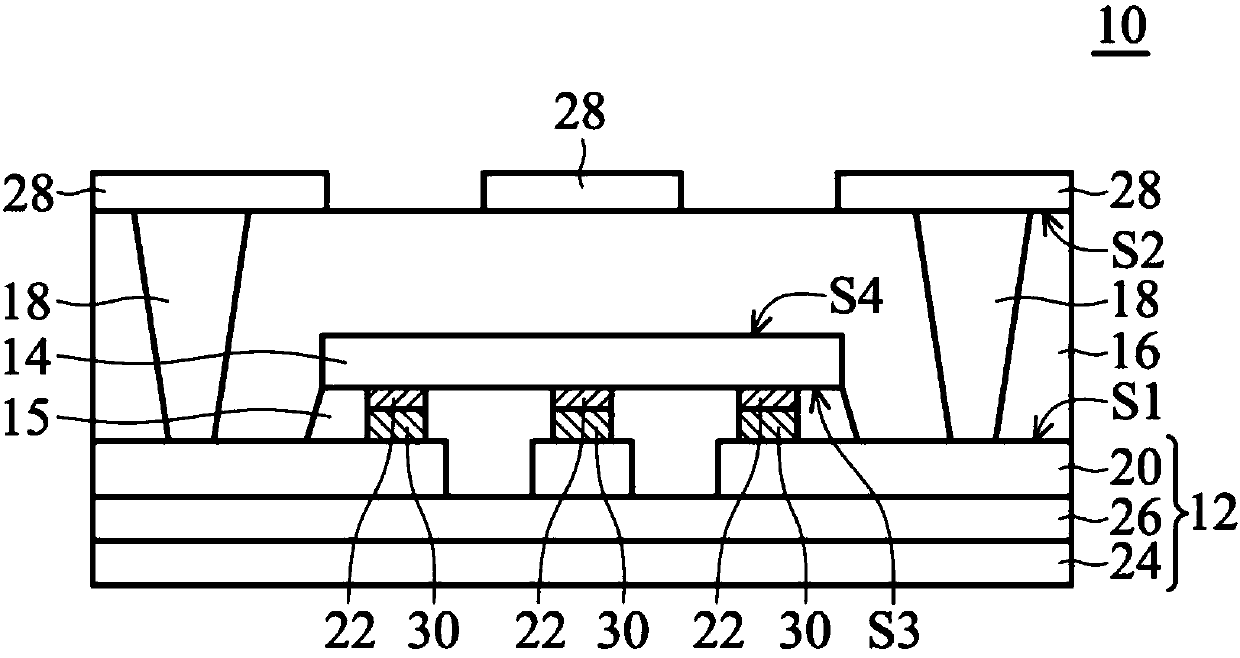

[0043] Figure 1 to Figure 4 It is a schematic cross-sectional view of a chip package module according to the first embodiment of the present invention.

[0044] Please refer to figure 1 , in this embodiment, the chip packaging module 10 includes a molding layer 16 , a chip 14 and a substrate 12 . The molding layer 16 has a first surface S1 and a second surf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com