A kind of semiconductor structure preparation method and semiconductor device

A technology of semiconductors and precursors, applied in the field of microelectronics, which can solve problems such as unexisting, extremely high process temperature requirements, and complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

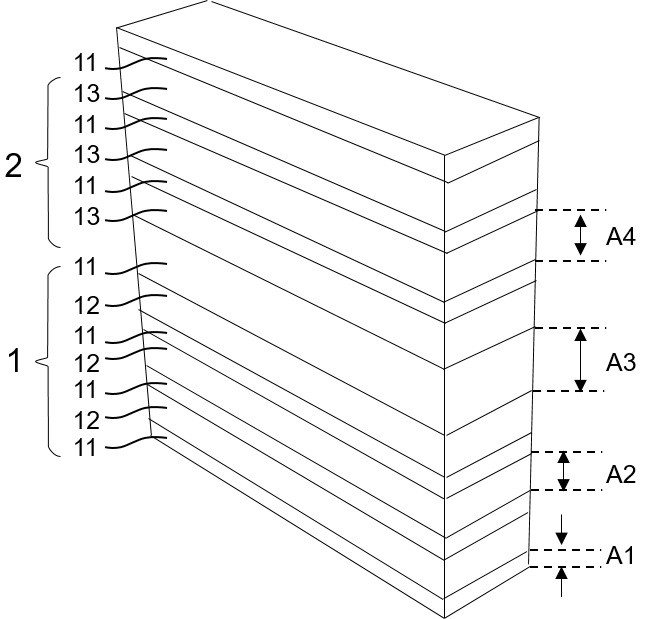

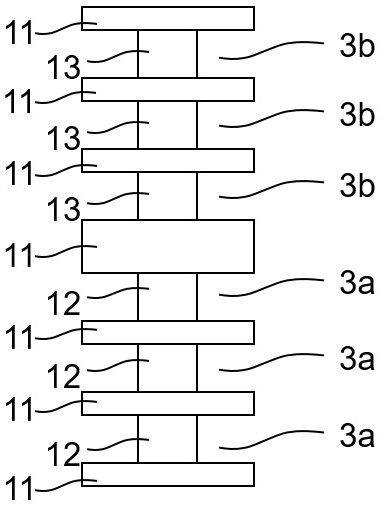

[0043] This embodiment first provides a method for simultaneously integrating P-type and N-type stacked nanowires in a three-dimensional direction, such as Figure 1a~1i As shown, the method includes at least the following steps:

[0044] The first step is to alternately deposit the first thin film layer 11 and the second thin film layer 12 to form the first base material layer 1; continue to alternately deposit the first thin film layer 11 and the third thin film layer 13 on the first base material layer to form The second base material layer 2 is formed.

[0045] The substrate layer is patterned to expose the first sidewall 100 of the first substrate layer in the stacking direction and the second sidewall 200 of the second substrate layer in the stacking direction. Using SF 6 or C 4 f 8 or CF 4 and other fluorine-containing plasma etching methods, etch downward along the edge of the pattern, etch the first and third film layers except the pattern coverage area, exposing...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com