Automatic generation method of variable bit width multiplier

A multiplier and variable technology, applied in the fields of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of insufficient flexible support for variable number of digits, and the configuration of pipeline stages has not been considered, and achieves a feasible solution. Configurable, flexible and universal effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

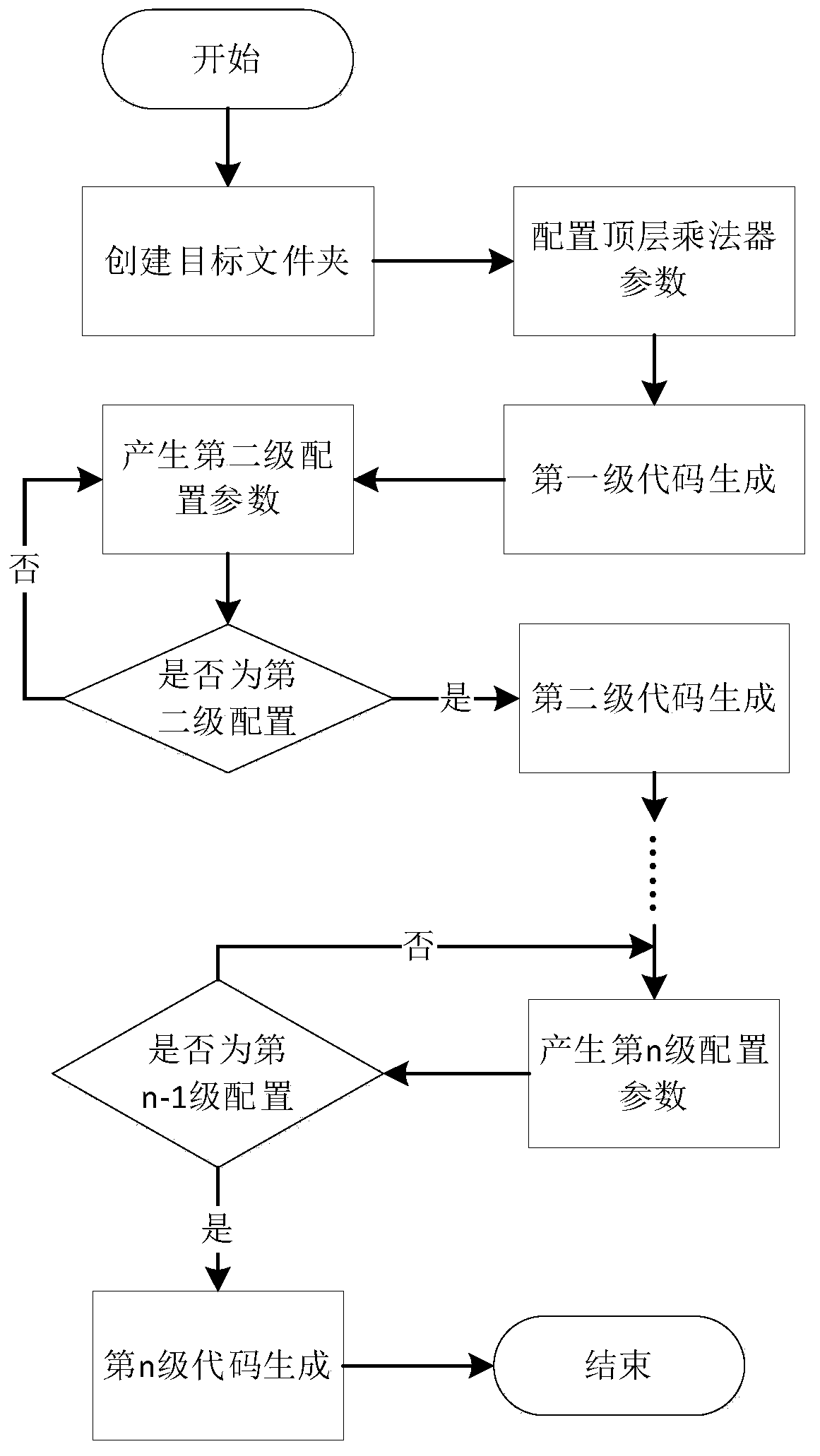

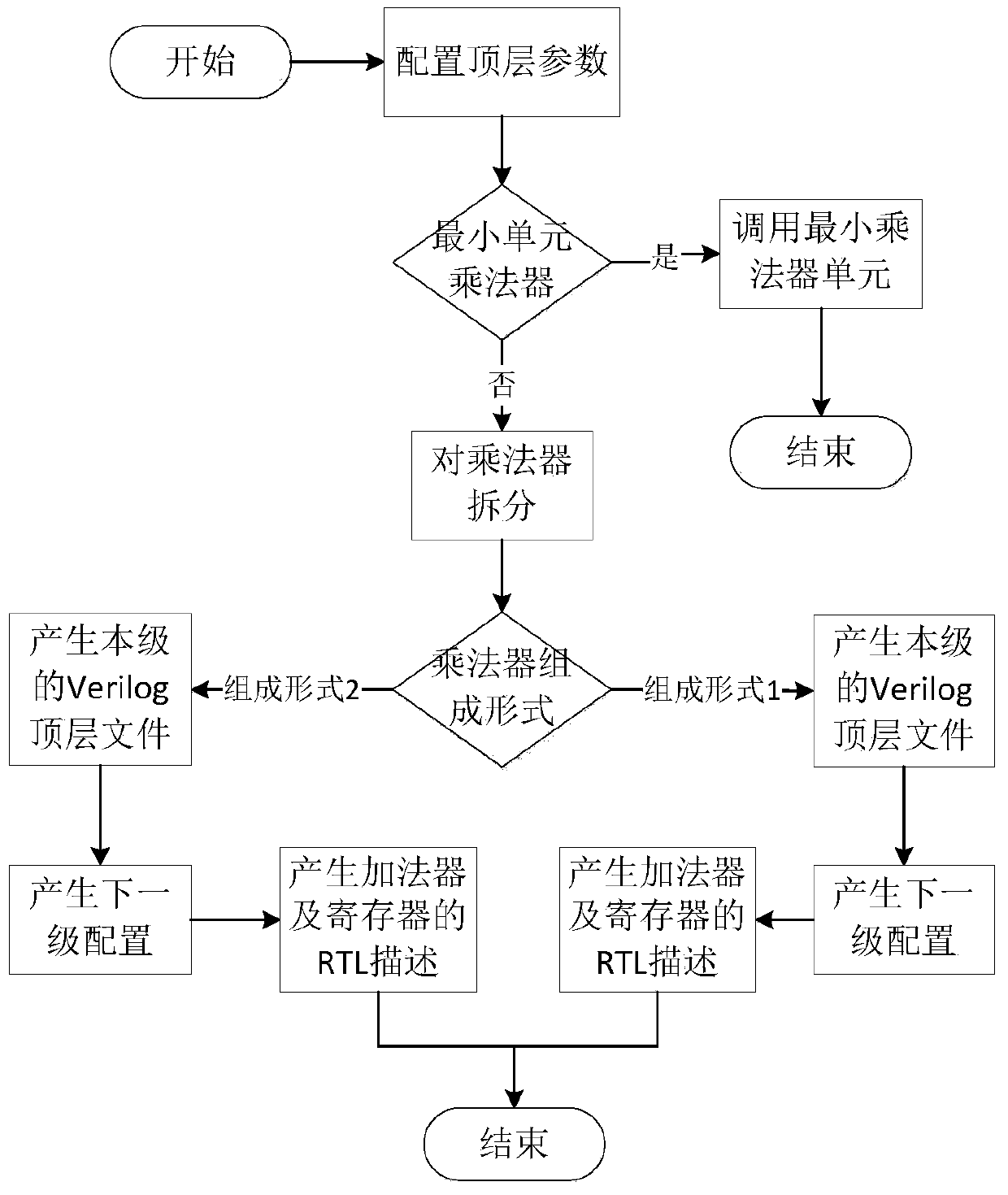

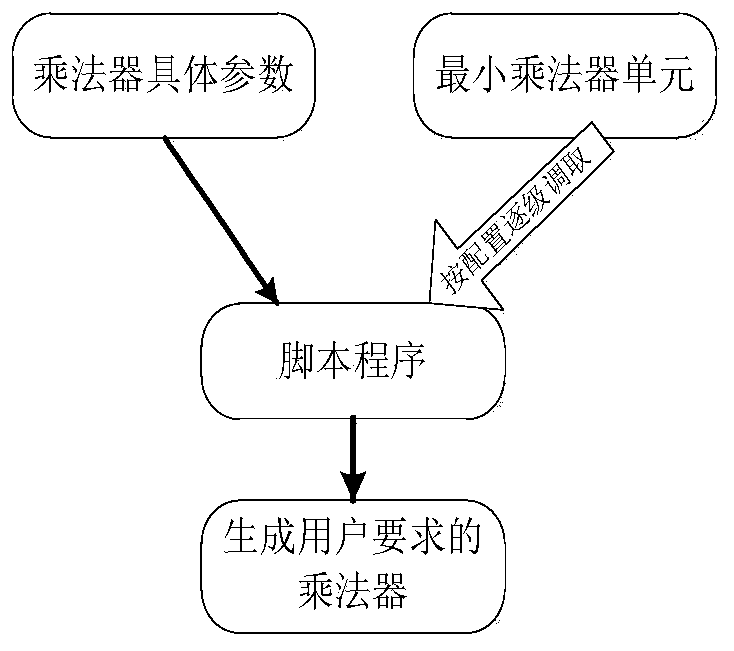

[0026] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. figure 1 For the quick generation flow chart of the multiplier proposed in this patent, the user creates the target folder, configures the required multiplier parameters, and then divides down step by step according to the nesting level of the multiplier listed in Table 3-4 and generates the corresponding RTL code until the divided unit is the smallest granularity unit, stop dividing, and complete the generation of the required multiplier RTL code. Specific steps are as follows:

[0027] Step 1: Create a target folder on the client side and configure the top-level multiplier parameters.

[0028] The top-level configuration file is a text file, which contains the parameters of the multiplier input by the user. These parameters need to be separated by spaces to be correctly recognized by the script. There are 9 parameters in it, and thei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com