Inverted T Tunneling Field Effect Transistor

A technology of tunneling field effect and transistor, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of low tunneling efficiency, low on-state current, large static power consumption of devices, etc., and achieve good gate control ability, Effect of Low Subthreshold Swing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the drawings and embodiments.

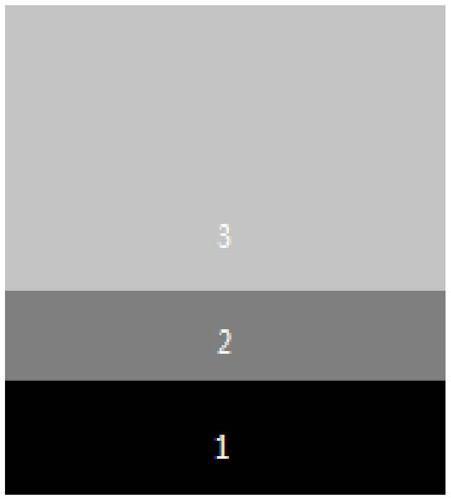

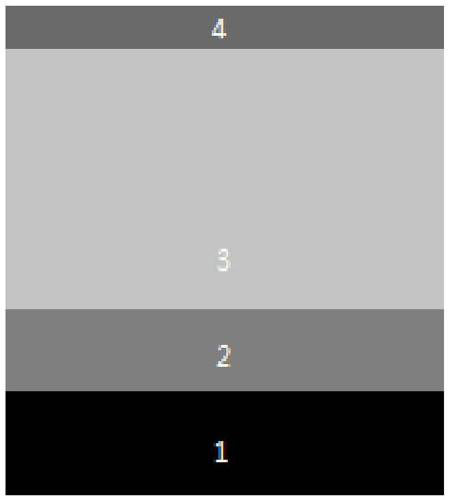

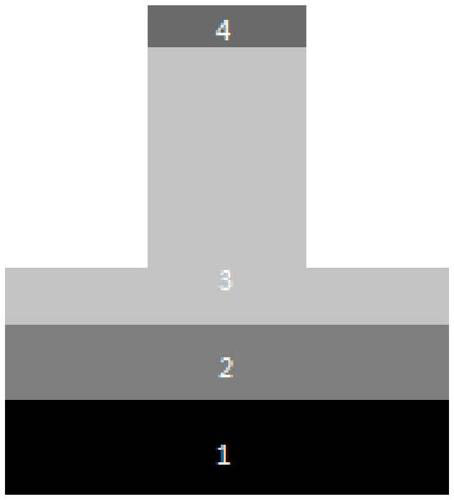

[0029] An inverted T tunneling field effect transistor, including the silicon substrate of the SOI wafer, the silicon substrate of the SOI wafer is the substrate insulating layer of the SOI wafer, and the substrate insulating layer of the SOI wafer is heavily doped Miscellaneous source region, two monocrystalline silicon films, and two heavily doped drain regions. The heavily doped source region is located in the middle above the insulating layer of the substrate. The two monocrystalline silicon films are both L-type and are located at the heavily doped source. The two heavily doped drain regions are located on the L-shaped bottom of the monocrystalline silicon film and are close to the outer edge of the lateral edge of the substrate insulating layer of the SOI wafer, and are located in the substrate insulating layer. Above; the two monocrystalline silicon film L-shape...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com