Array substrate and manufacturing method thereof

A technology for array substrates and manufacturing methods, applied in the direction of exposure devices, optics, instruments, etc. in photolithography, can solve the problems of increased process steps and lower yields, and achieve cost savings, large pixel aperture ratios, and reduced number of masks Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

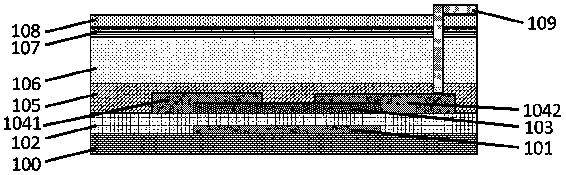

[0046]The array substrate of the present invention includes: criss-cross scan lines and data lines, a pixel area defined by intersections of the scan lines and data lines, a thin film transistor located in the pixel area, and a planarization layer 06 . The thin film transistor is a multi-layer thin film transistor, that is, in the same projected area (x / y plane), at least two thin film transistors arranged one above the other in the z space are provided.

[0047] Such as figure 2 As shown, the multilayer thin film transistor in this embodiment includes a first thin film transistor located on the base substrate 200, and a second thin film transistor located above the first thin film transistor, and the planarization layer 06 is located between the first thin film transistor and the second thin film transistor. between thin film transistors. The first thin film transistor includes, from bottom to top: a first gate 01A located on the substrate 200, a first gate insulating layer...

Embodiment 2

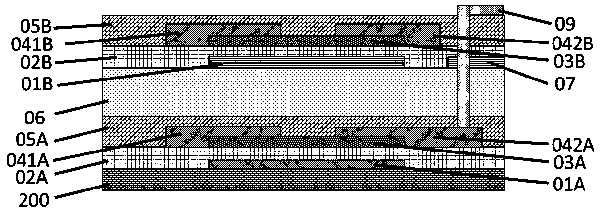

[0077] Figure 7 Shown is a schematic structural diagram of an array substrate according to Embodiment 2 of the present invention. The difference from Embodiment 1 is that both the first thin film transistor and the second thin film transistor in the multilayer thin film transistor of Embodiment 1 adopt a bottom gate structure. Both the first thin film transistor and the second thin film transistor in the multilayer thin film transistor of the embodiment adopt a top-gate structure.

[0078] It should be noted that the multi-layer thin film transistor of the array substrate of the present invention includes a plurality of thin film transistors arranged in layers above and below in the z space, and the plurality of thin film transistors can be independently set as top gates, bottom gates, BCE (back channel channel etching type), ESL (channel protection type) and other transistor types.

[0079] Such as Figure 7 As shown, the multilayer thin film transistor in this embodiment ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com