Integrated circuit chip packaging structure and manufacturing method thereof

A technology of integrated circuit and packaging structure, which is applied in the direction of circuits, electrical components, electric solid devices, etc., can solve problems such as permanent failure, user loss, and short-term failure, so as to prolong low-temperature life, prevent short-term failure or permanent failure, and reduce low-temperature failure. The effect of error rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

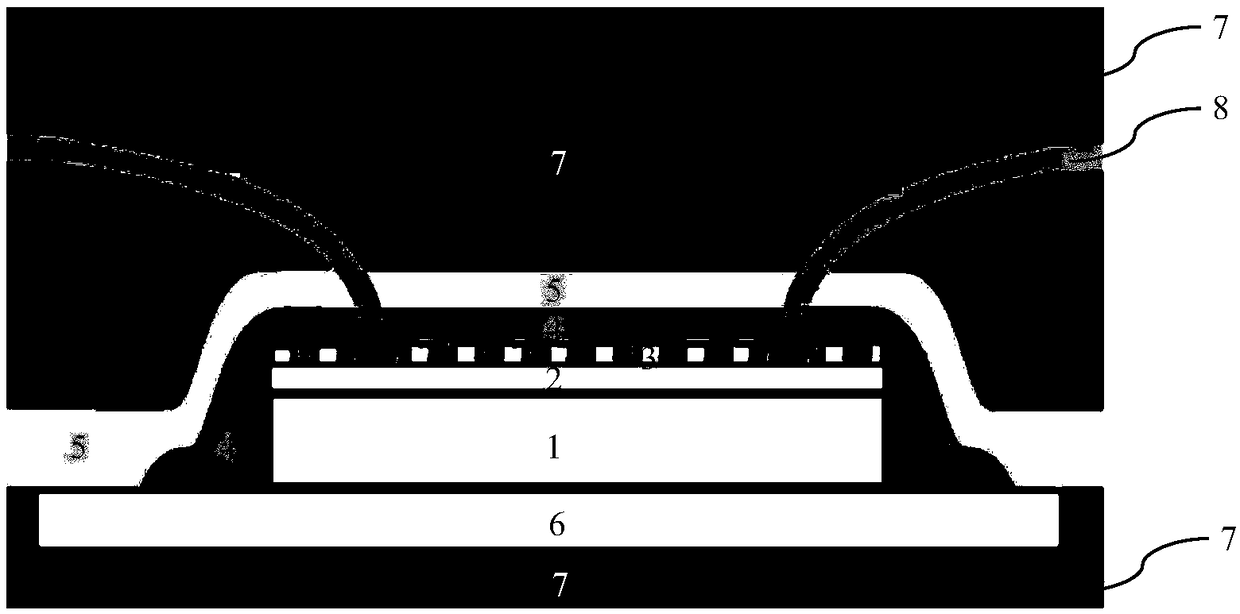

[0033] Such as figure 1 As shown, it is a schematic structural diagram of the packaging structure of the integrated circuit 2 chip 1 in the embodiment of the present invention. In the packaging structure of the integrated circuit 2 chip 1 in the embodiment of the present invention, the integrated circuit 2 on the chip 1 includes a temperature-sensitive circuit. Sensitive circuitry increases chance of failure as operating temperature decreases; package construction includes:

[0034] A heat conduction layer 4, the heat conduction layer 4 completely covers at least the front and side surfaces of the temperature sensitive circuit.

[0035] The heat insulating layer 5 is formed on the surface of the heat conducting layer 4 and covers the heat conducting layer 4 .

[0036] The heat-conducting layer 4 forms a structure that makes the temperature of each position of the area covered by the heat-conducting layer 4 uniform, and the heat-insulating layer 5 forms a structure that preven...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com