Full-chip electrostatic discharge network

An electrostatic discharge, full-chip technology, applied in circuits, electrical components, electric solid devices, etc., can solve problems such as not helping to discharge electrostatic charges, affecting the anti-static ability of devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

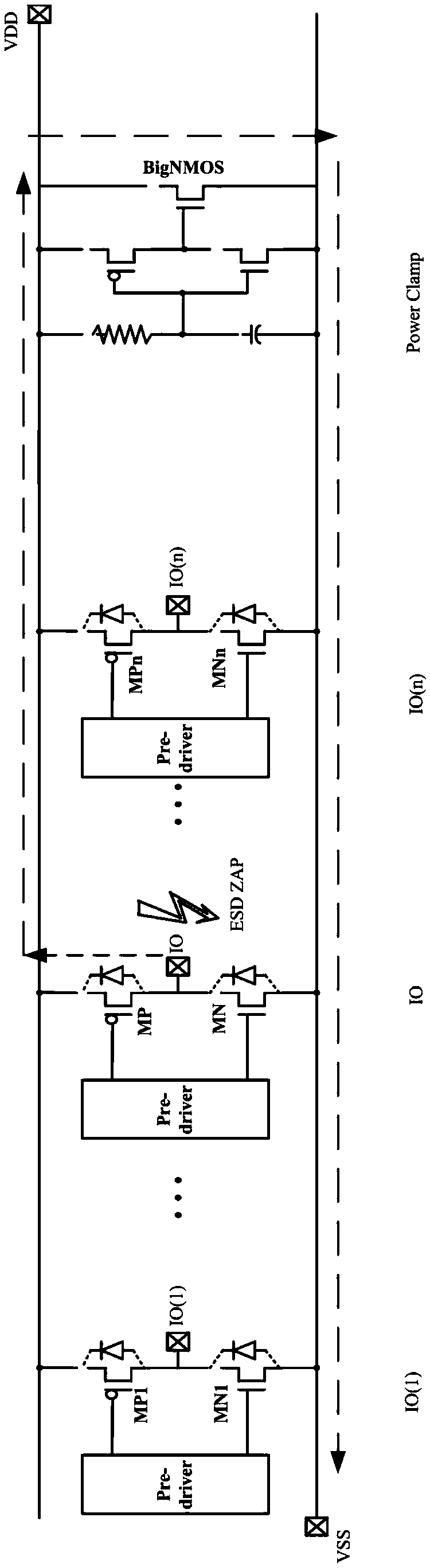

[0020] The full-chip electrostatic discharge network of the present invention, such as figure 2 As shown, it includes a power clamp circuit (PowerClamp) and multiple identical IO units connected in parallel.

[0021] The power supply clamping circuit is connected between the power supply and the ground, and the power supply clamping circuit also includes an ESD detection circuit for detecting ESD signals, and will generate a trigger signal after detecting the ESD signals; It also includes an electrostatic discharge transistor, and the detected ESD signal is simultaneously provided to the gate of the electrostatic discharge transistor. This transistor is used to release the static electricity on the power supply to the ground line, and this transistor is an NMOS transistor (BigNMOS) whose size is much larger than other transistors.

[0022] The multiple IO units include n identical units from IO(1) to IO(n), which are connected in parallel and then connected in parallel with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com