Test method and system based on SPARC (Scalable Processor ARChitecture) processor single event upset fault injection

A single event inversion and fault injection technology, applied in the detection of faulty computer hardware, electrical digital data processing, instruments, etc., can solve the problems of lack of fault injection, insufficient ground test verification, lack of single event fault, etc. Flexible, modeling high-speed operation, improving reliability and safety validation testing and verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

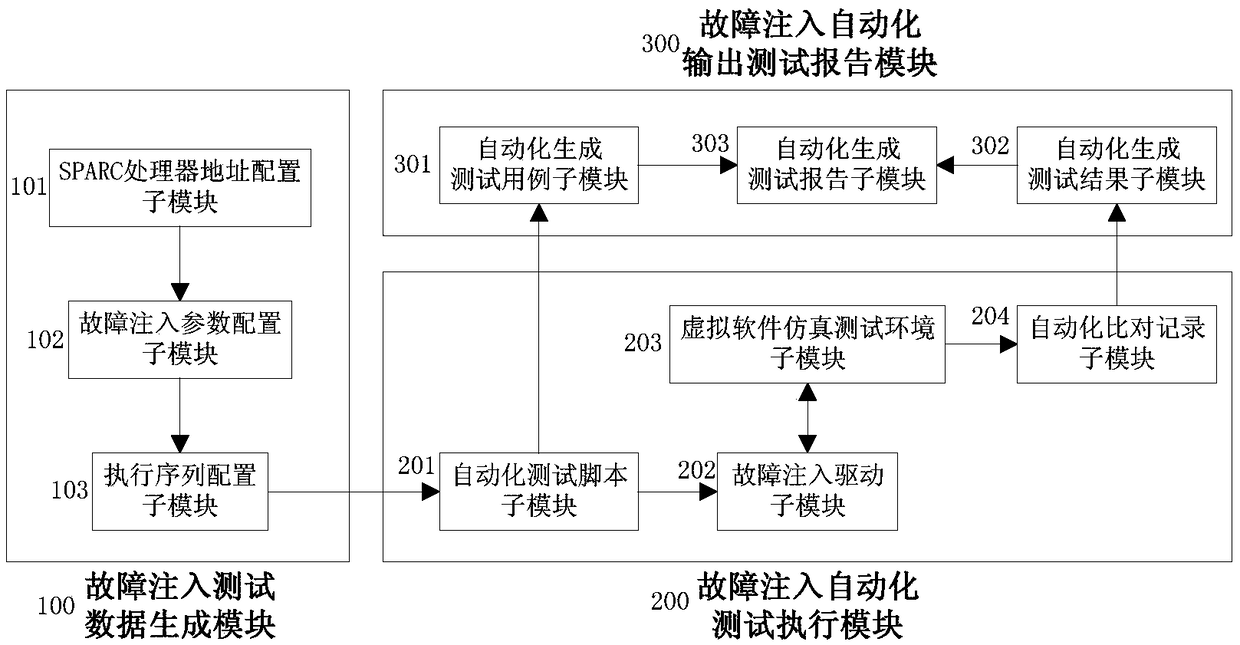

[0035] Such as figure 1 Shown is a block diagram of the fault injection automated testing method of the present invention, step 100 fault injection test data generation module includes: SPARC processor address configuration sub-module, fault injection parameter configuration sub-module, execution sequence configuration sub-module.

[0036] Step 101 SPARC processor address configuration sub-module: the SPARC processor type can be selected from TSC695, BM3803, AT697, SOC2008, SOC2012. The SRAM memory includes the SRAM area, the SRAM program area, the SRAM three-out two area one, the SRAM three-out two area two, and the SRAM three-out two area three. EEPROM memory includes primary EEPROM, backup EEPROM, and other storage areas. Non-writable areas include PROM area and SRAM write-protected area. SRAM and EEPROM can configure the start address and end address.

[0037] Step 102 The fault injection parameter configuration sub-module includes: fault injection single fault configur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com