Latch circuit

A latch circuit, latch technology, applied in the direction of analog-to-digital converter, reliability improvement and modification, etc., can solve the problem of high contribution ratio of analog-to-digital converter, reduction of resolution of analog-to-digital converter, and reduction of comparator Bit resolution, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The circuit composition and connection mode of the present invention are further described in conjunction with the drawings and specific embodiments, and the beneficial effects of the present invention are also illustrated.

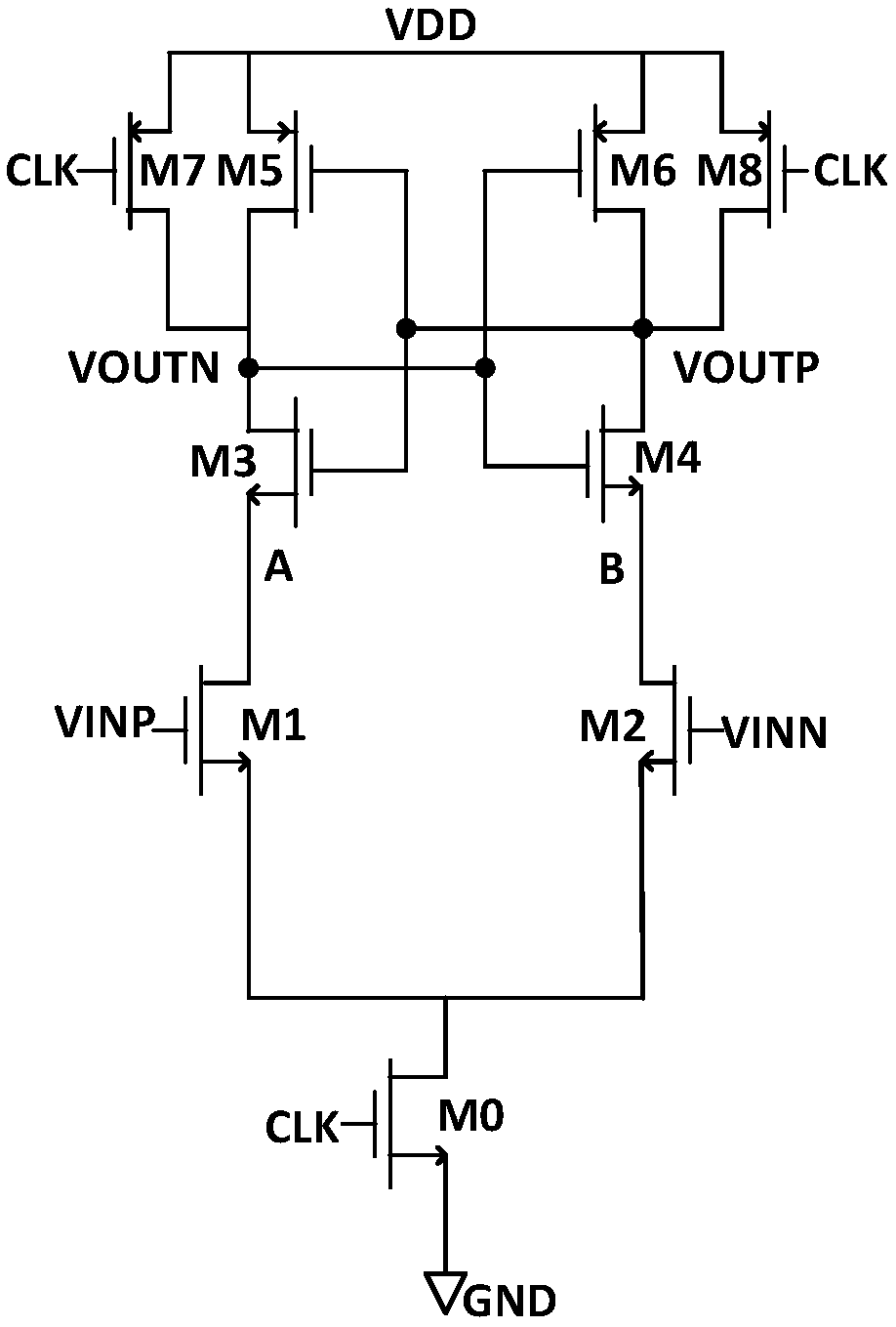

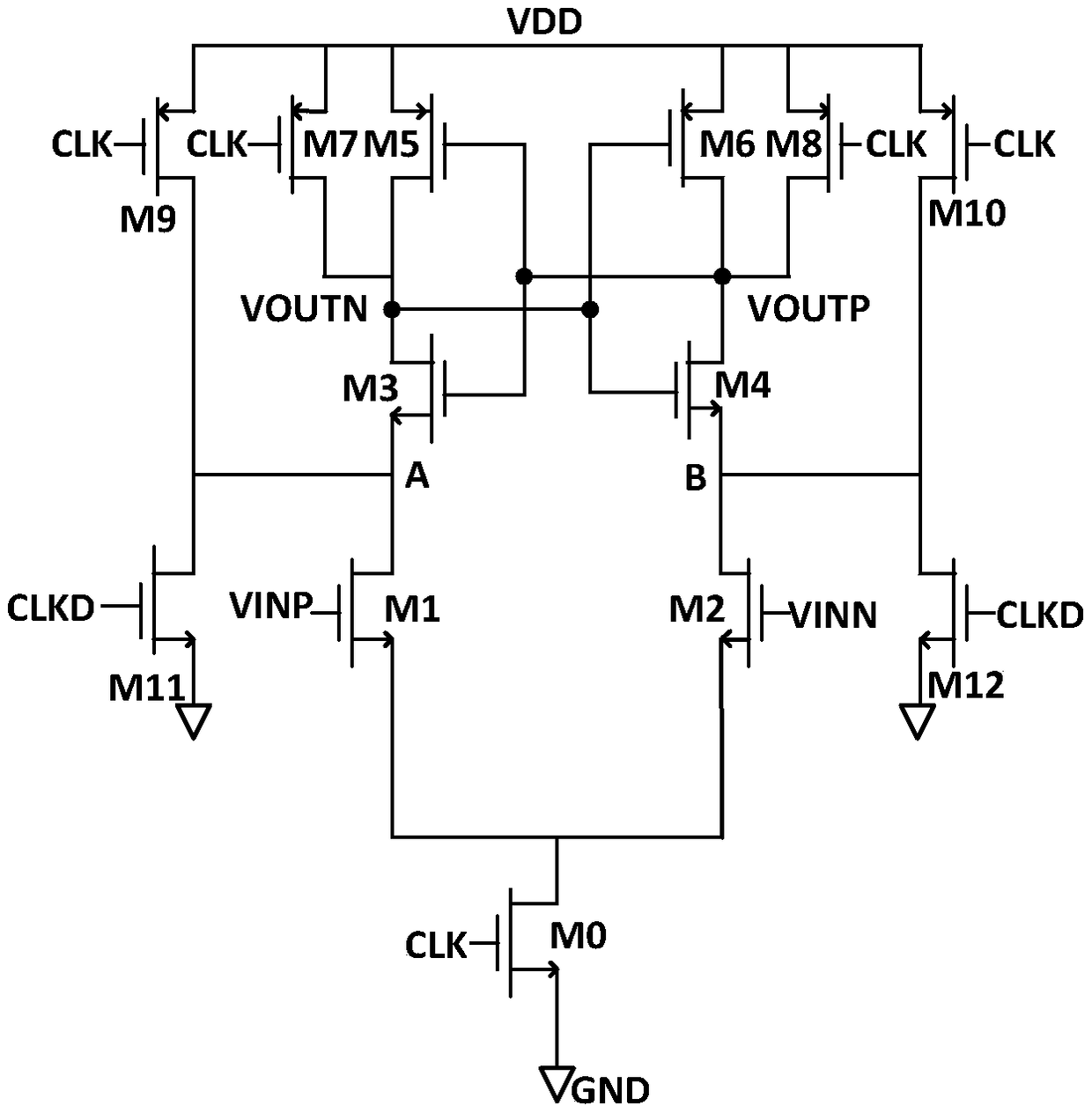

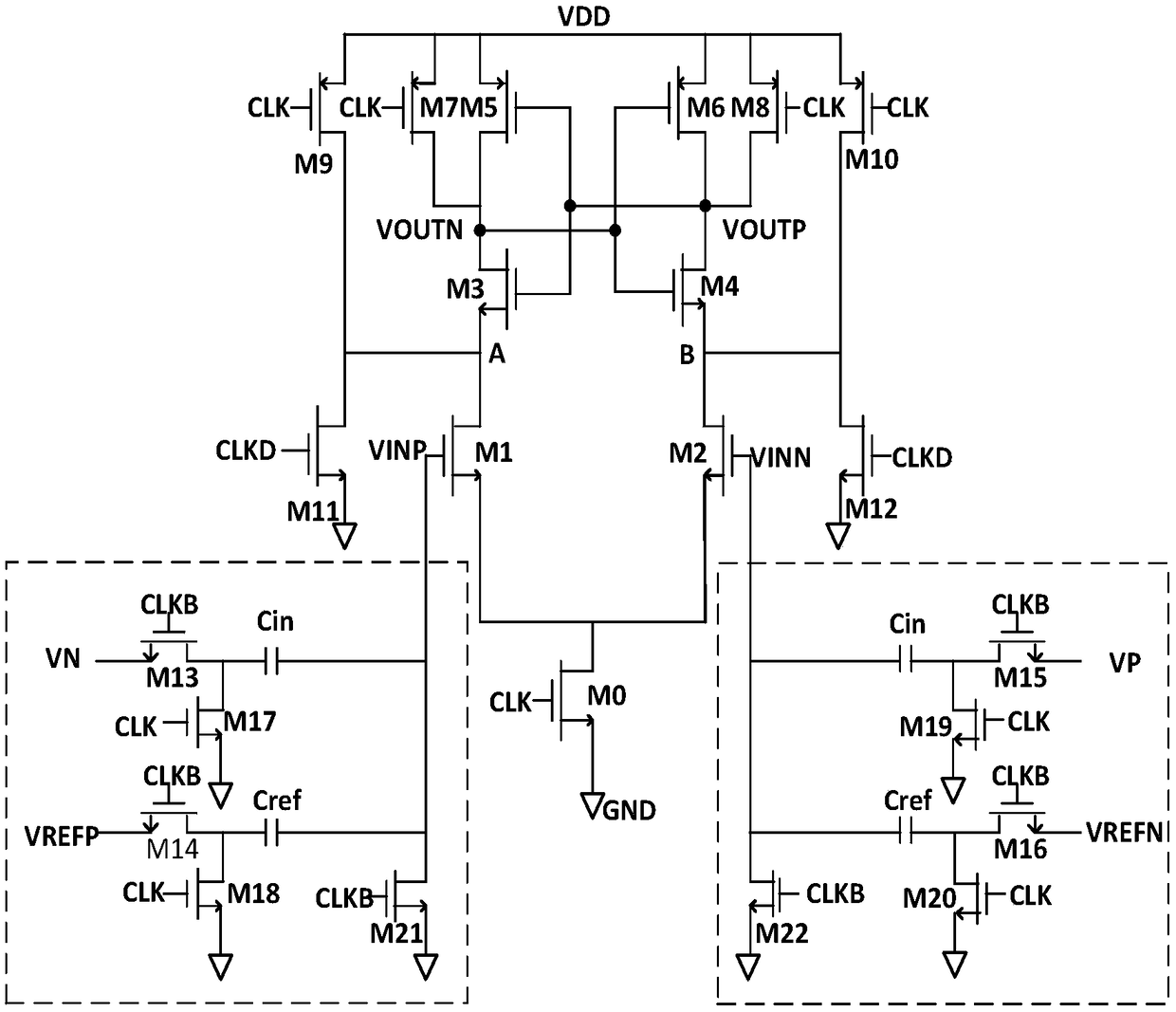

[0047] Such as figure 2 As shown, a latch circuit provided by the present invention includes: a current tail pipe—a third NMOS transistor (M0); the preamplifier consists of a fourth NMOS transistor (M1) and a fifth NMOS transistor (M2) The gates of the fourth NMOS transistor (M1) and the fifth NMOS transistor (M2) are connected to the differential signal VINN and VINP, and the differential signal is amplified to the A and B terminals; the main body of the comparison latch includes A CMOS comparison latch, the CMOS comparison latch is composed of the fifth PMOS transistor (M5), the sixth PMOS transistor (M6), the sixth NMOS transistor (M3), and the seventh NMOS transistor (M4). The latch latches the amplified differential signal. The aforementioned...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com