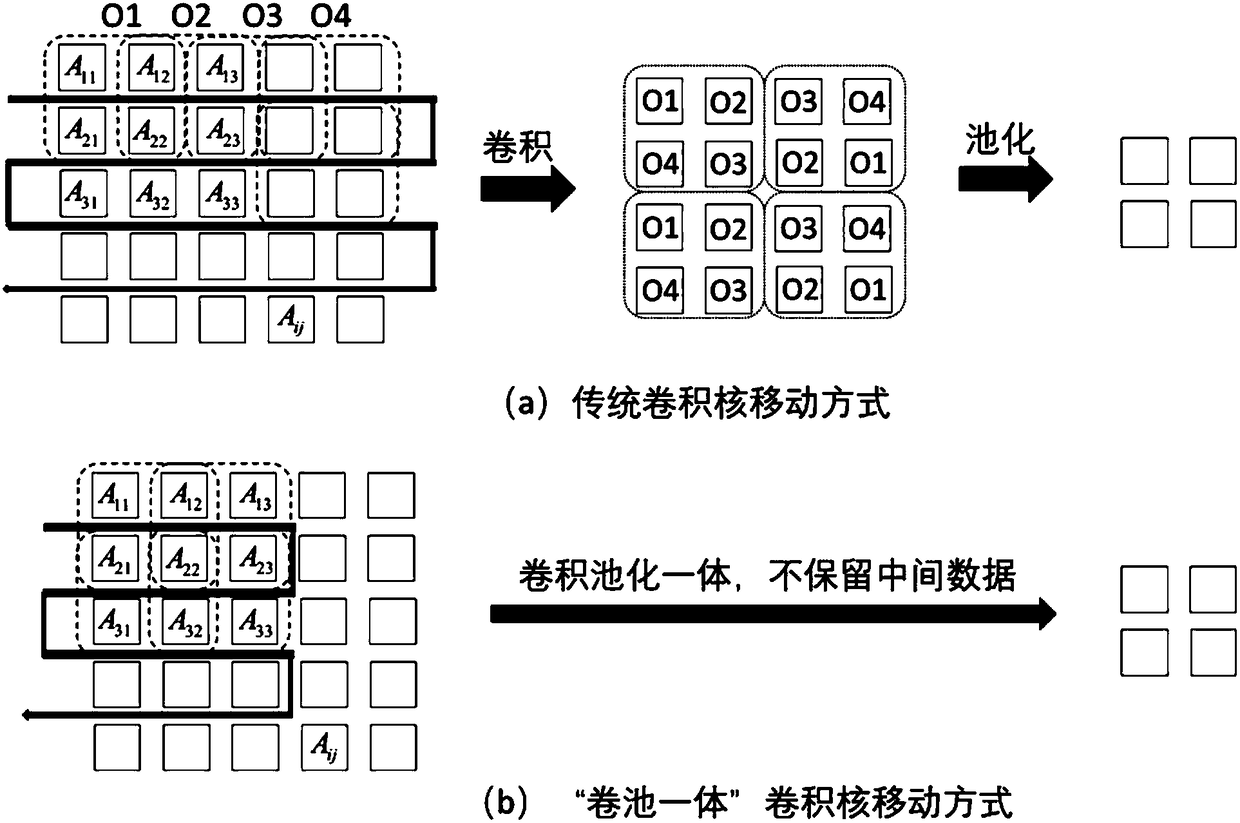

Reconfigurable convolutional neural network acceleration circuit based on asynchronous logic

A convolutional neural network and asynchronous logic technology, applied in the field of reconfigurable convolutional neural network acceleration circuits, to achieve standardized network interfaces, low energy consumption, and low system integration complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The implementation of the present invention will be described in detail below in conjunction with the drawings and examples.

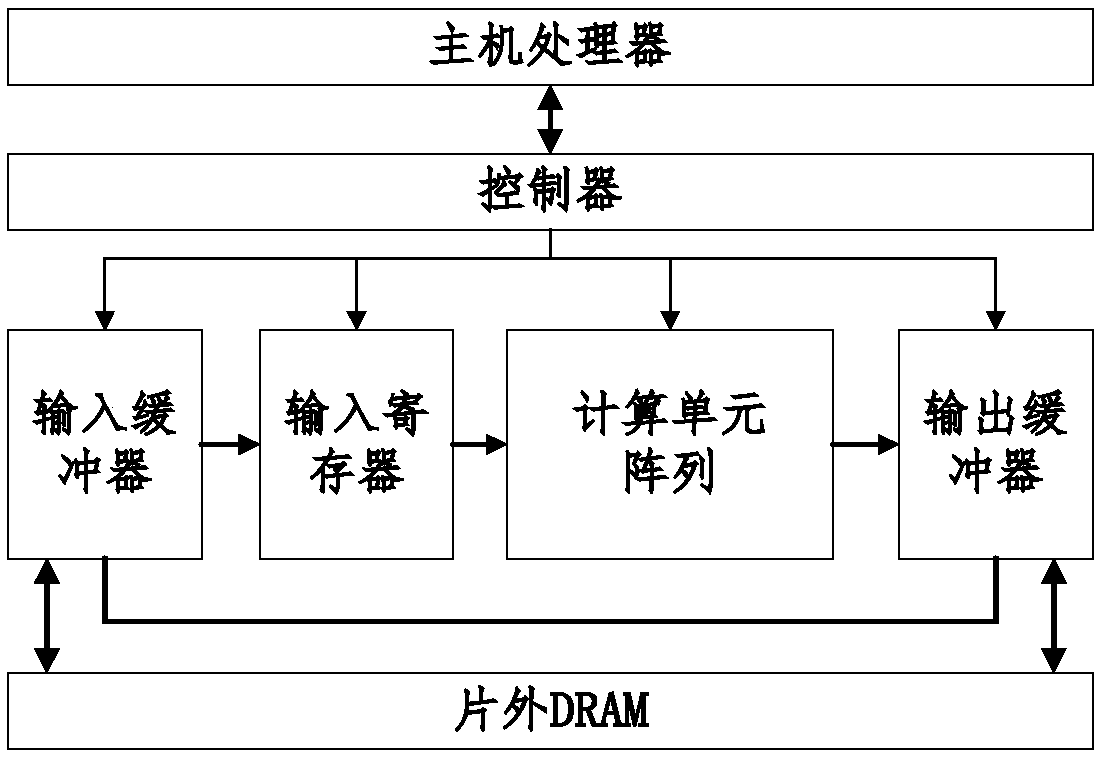

[0032] Such as figure 1 As shown, the input data is stored in the off-chip DRAM. Before each operation, the controller first writes the configuration information into the computing unit array. The configuration information determines the scheduling method of the computing unit array and the data multiplexing method. Due to the short time required for this configuration, dynamic configuration is possible, either according to different CNN models or according to different layers of the same model. The data to be processed is read into the input buffer and input register (Mesh architecture), then enters the computing unit array for processing, and finally obtains the output data through the output buffer.

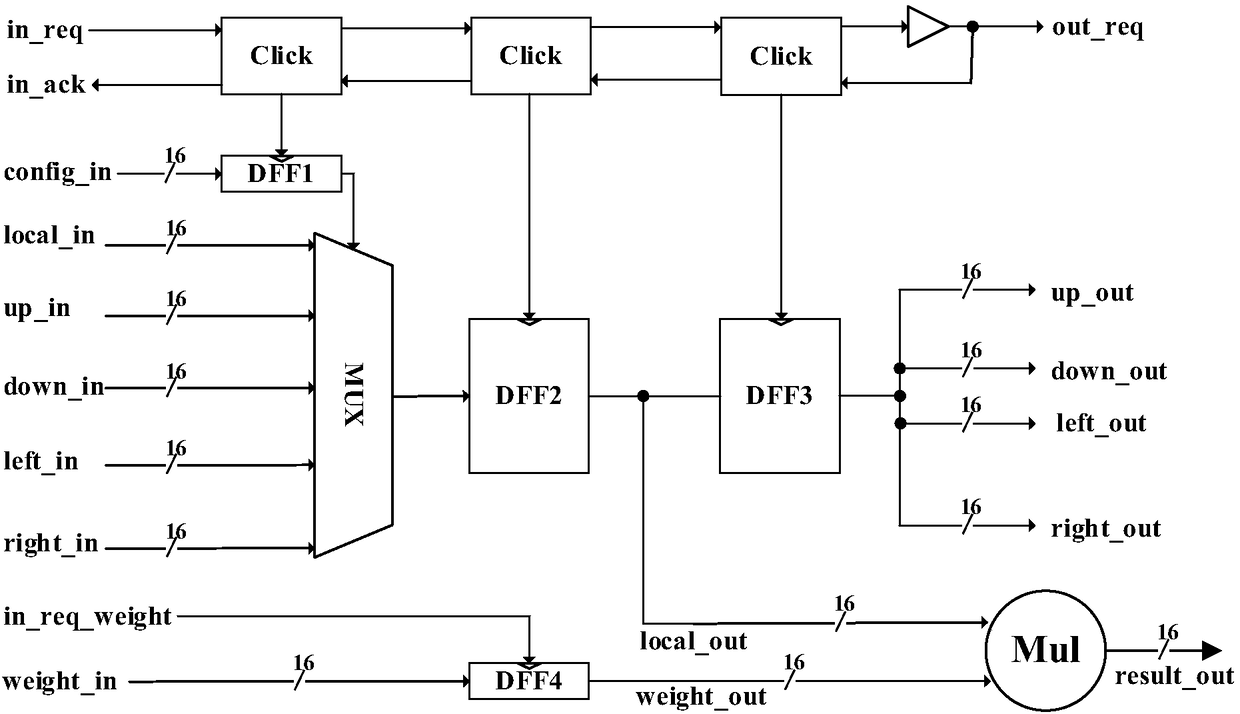

[0033] The basic operation unit (PE) based on asynchronous logic such as figure 2 As shown, the control part of the PE is a three-stage asyn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com