A Distributed Computer Network Clock Synchronization Delay Compensation Method

A computer network and clock synchronization technology, applied in time-division multiplexing systems, electrical components, multiplexing communications, etc., can solve the problems affecting the synchronization accuracy of the system clock, the transmission delay cannot be determined, and improve the system time synchronization. The effect of precision, precise delay, and reduced clock synchronization requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

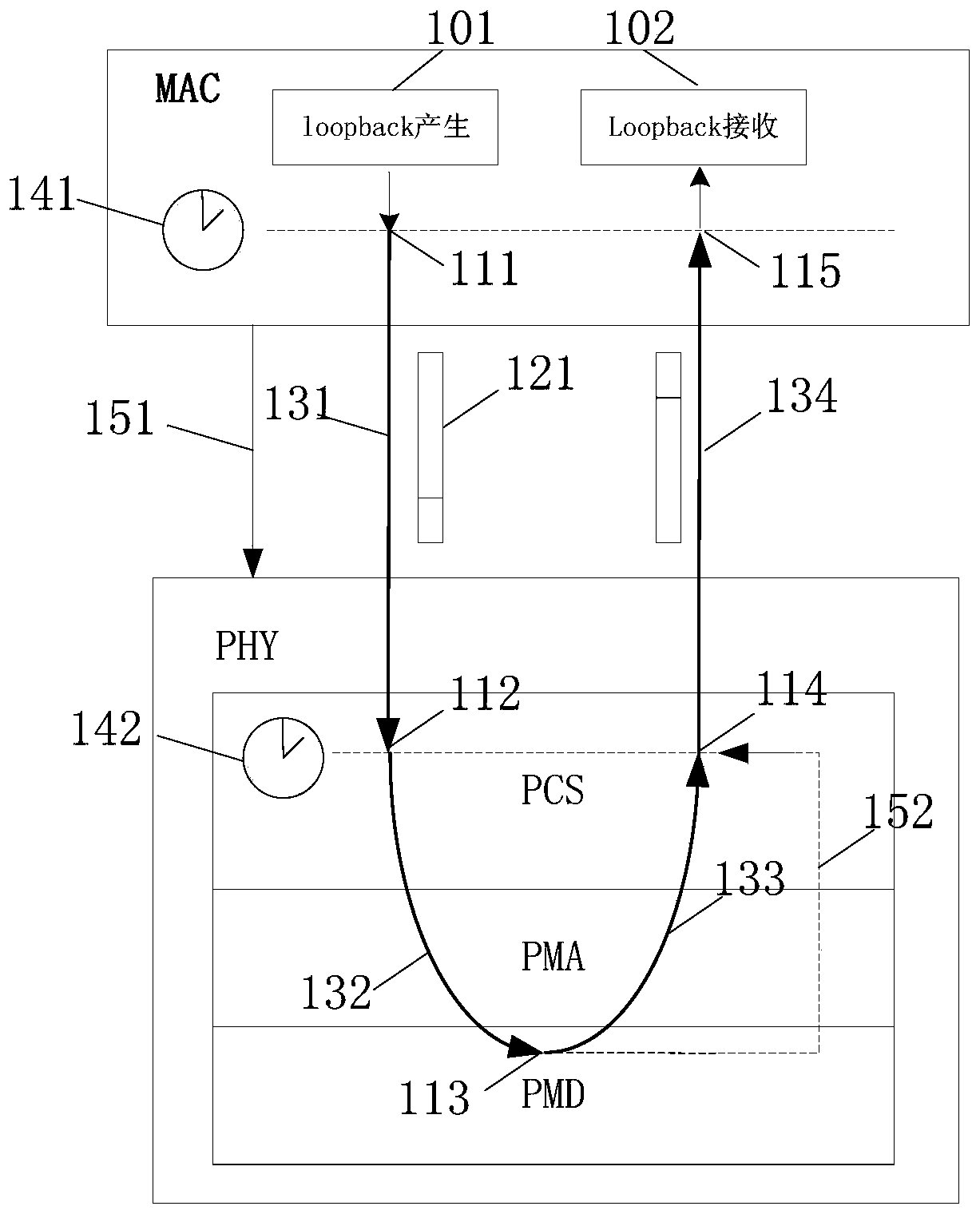

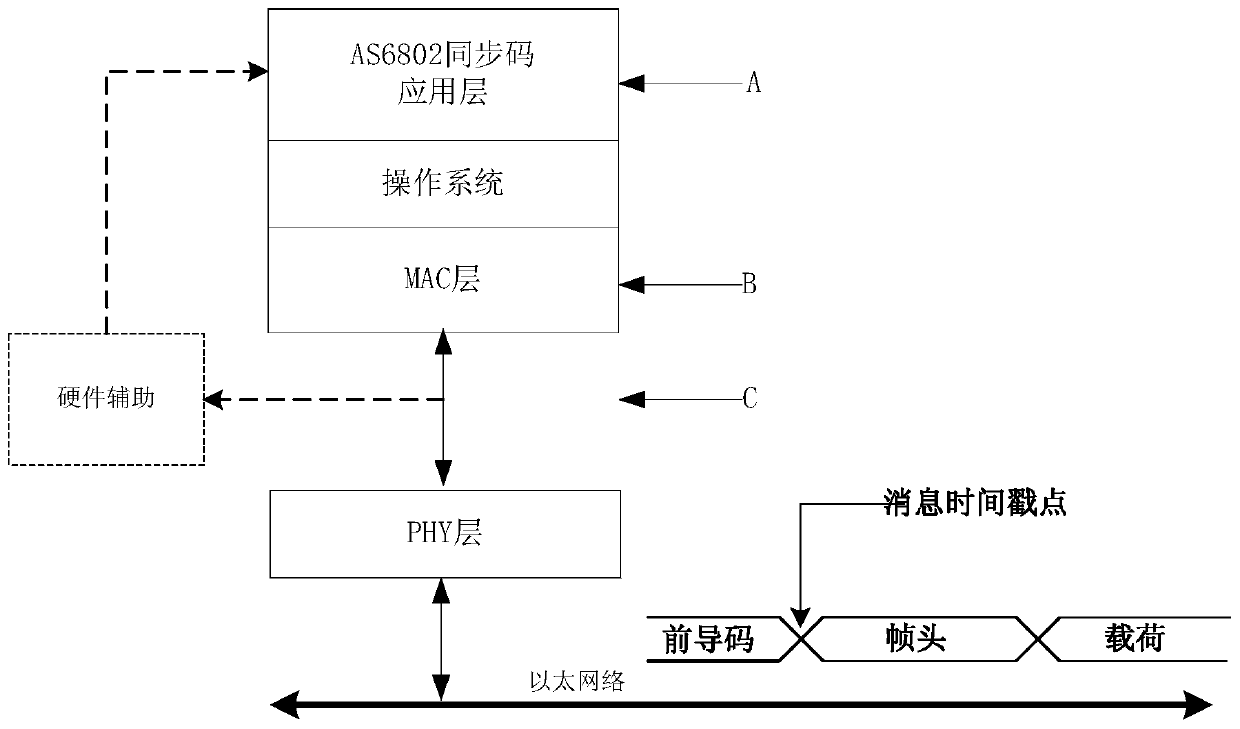

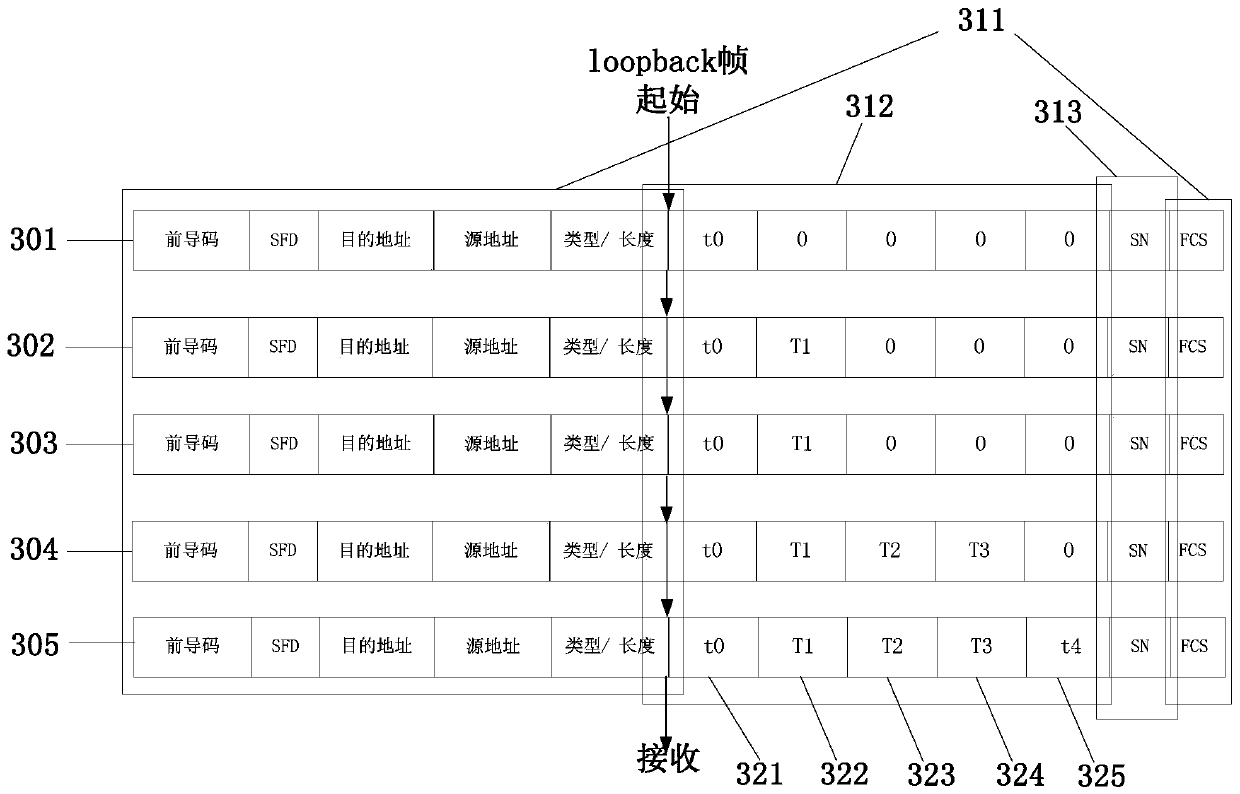

[0056] The present invention assumes that the link between the MAC and the PHY is symmetrical, and the path of receiving and sending inside the PHY chip is asymmetrical. In the loopback mode of the PHY, it is realized by sending a loopback frame through the MAC layer, and the calculation is performed after power-on and reset, and the chain There is no need to repeat the calculation when the circuit works normally, and only some adaptive modifications need to be made to the MAC layer and the PHY chip. Specifically include:

[0057] The mode setting (151), provided by the MAC layer, needs to combine the PHY state configuration of the application layer with the PHY state configuration generated by the delay calculation module to generate a new PHY state configuration signal.

[0058] The PHY works in loopback mode, the receiver between the PHY and the network cable will be turned off, and the PHY will not receive data from the network cable. This mode is used for the normal test ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com