Clock and data recovery circuit without reference clock input

A reference clock and recovery circuit technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of frequency tracking loop and phase tracking loop mutual interference, FD630 can not be adjusted normally, high production cost requirements, etc., to achieve Widen the operating frequency range, avoid lock-out phenomenon, and save chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

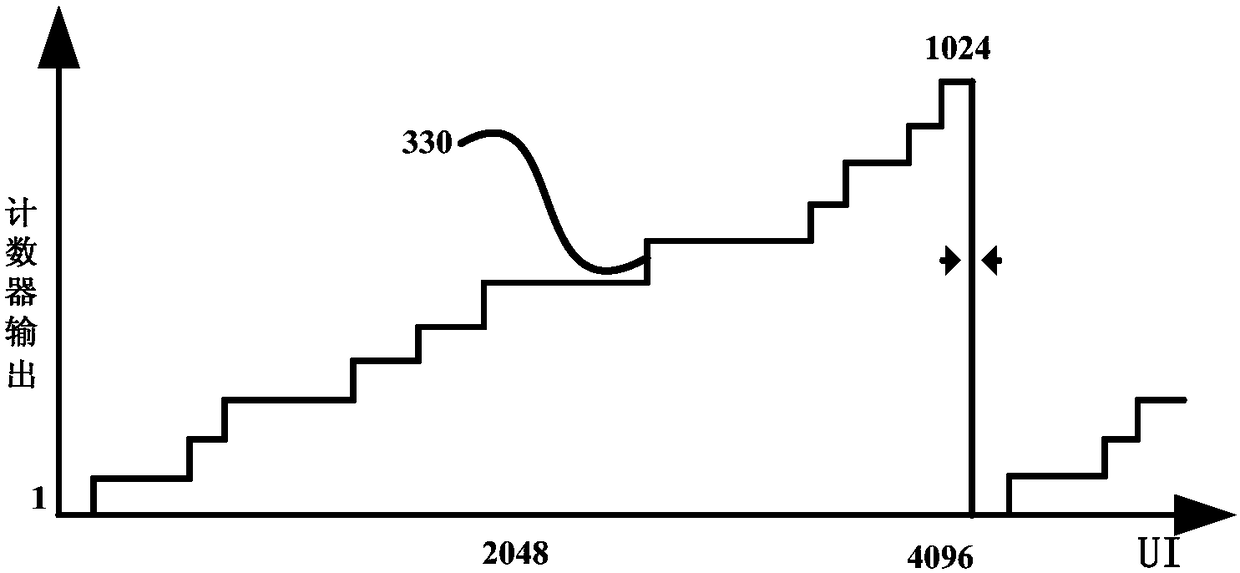

[0048] The invention provides a clock and data recovery circuit applied to high-speed interface circuits without reference clock input, combined with figure 1 The circuit includes high speed sampler 150, high speed sampler 210, buffer 110, binary phase detector 220, counter 120, count 160, comparator 130, digital filter 230, current steering DAC 190, voltage manager 180, low phase noise wide frequency VCO 170 and pseudo binary search algorithm module 140 .

[0049]The high-speed samplers 150 and 210 have the same structure, including two parts of a sense amplifier and an RS latch. The sampling rate is greater than 10Gbps. The Clk terminal is connected to the output of the VCO. When the Clk is low, the sampling unit is in the reset state, and the RS latch is in the Hold the state, the output remains unchanged from the previous state; when...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com