An overall fpga automatic layout method based on analytical methods

A technology of analysis method and layout method, which is applied in the direction of instrumentation, calculation, electrical digital data processing, etc., can solve problems such as difficult to meet timing constraints, and achieve the effect of optimizing quality and speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

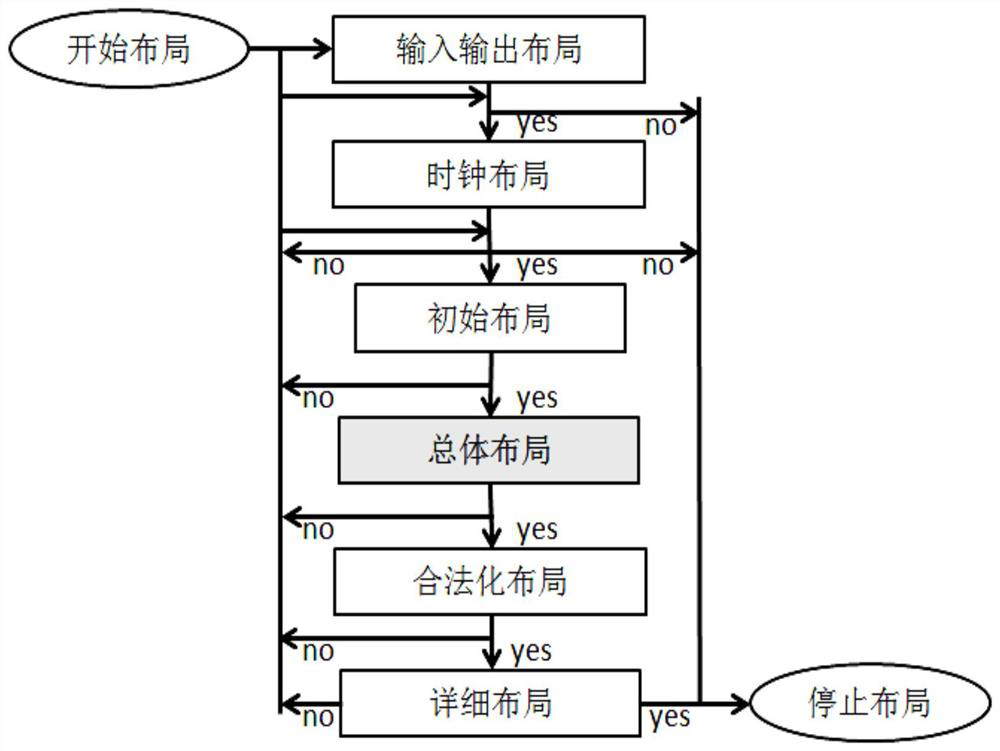

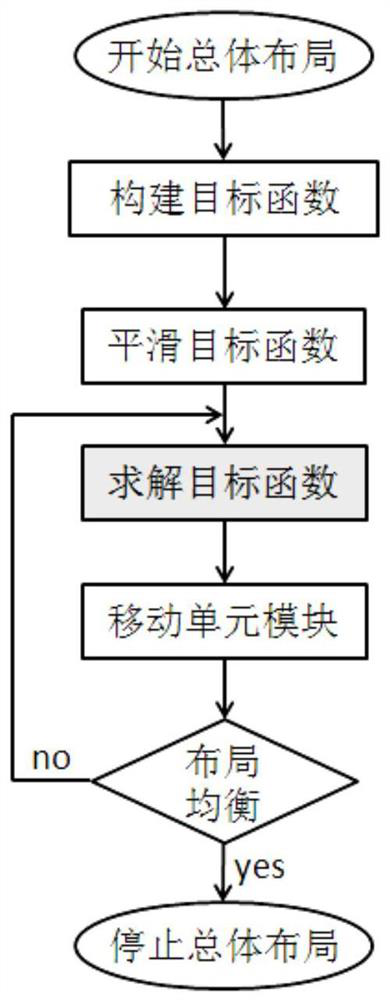

[0039] The following combination Figure 1 to Figure 6 , the present invention will be further elaborated by specifying a preferred specific embodiment.

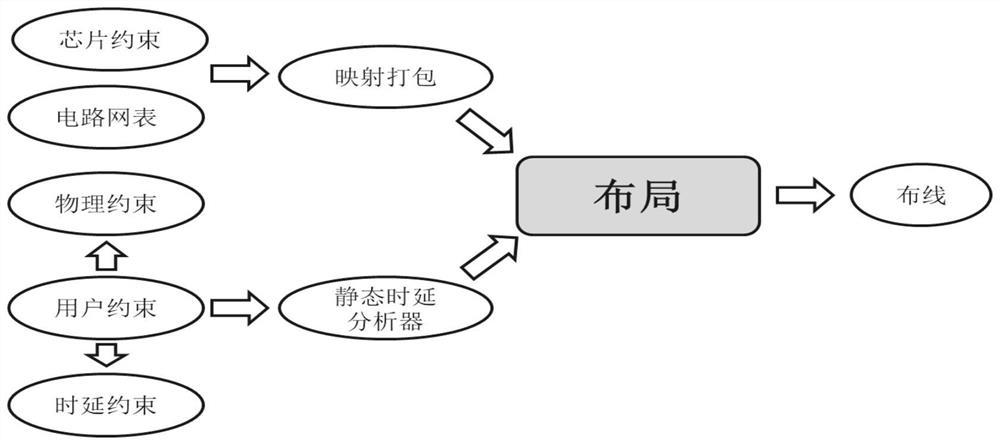

[0040] Such as figure 1 Shown, the design flowchart of the overall FPGA automatic layout method based on the analysis method provided by the present invention comprises the following steps:

[0041] S1. Pack and input FPGA chip constraint information and circuit netlist information through mapping;

[0042] S2. Inputting the user-constrained delay information of the FPGA through a static delay analyzer;

[0043] S3. According to the input chip constraint information, circuit netlist information and user constraint information, each circuit unit module is automatically placed in the corresponding position in the entire chip physical design, specifically including sequential input and output layout, global clock layout, and initial layout. , overall layout, legalized layout and detailed layout;

[0044] S4. Outputting the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com