Caching multi-bit hard error detection and fault tolerance device and method under near threshold voltage

A high-speed cache and threshold voltage technology, applied in the direction of error detection/correction, redundant code error detection, response error generation, etc., can solve the problems of lack of efficiency and reliability, and achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

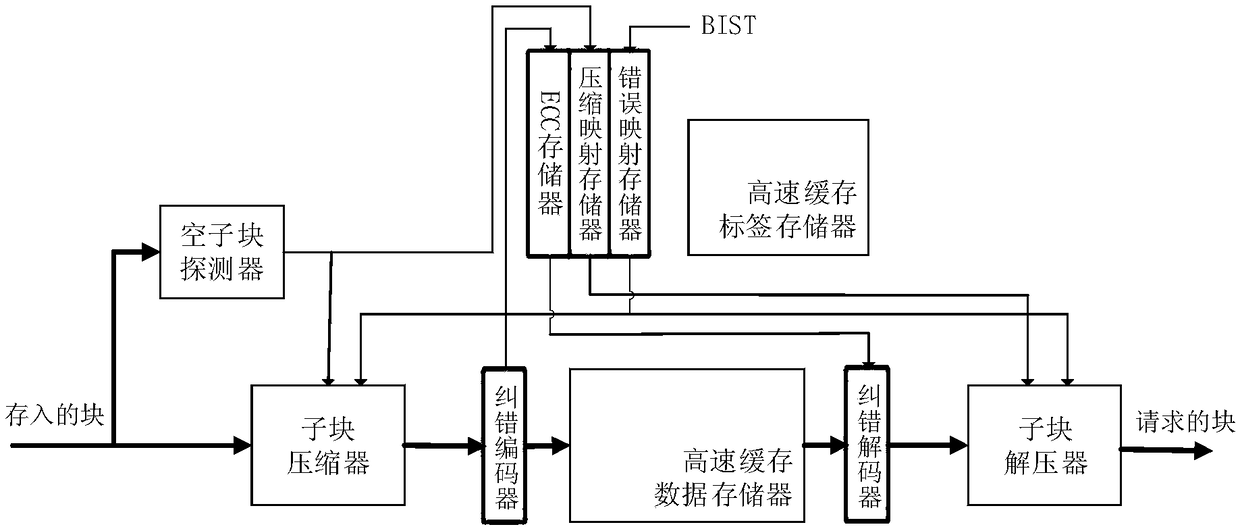

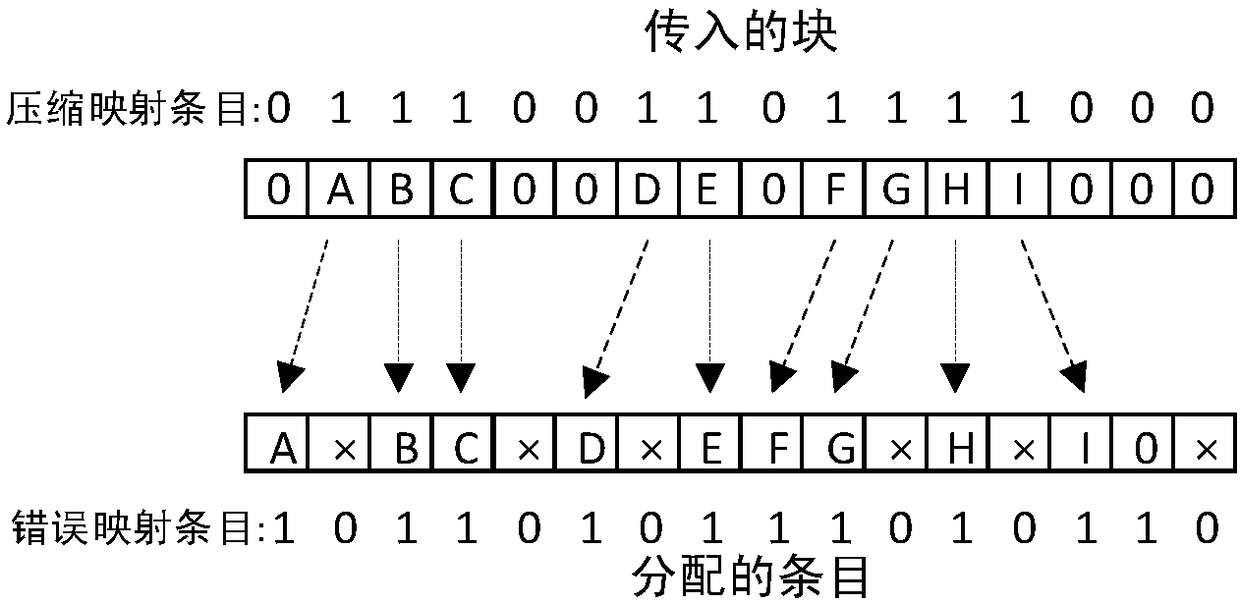

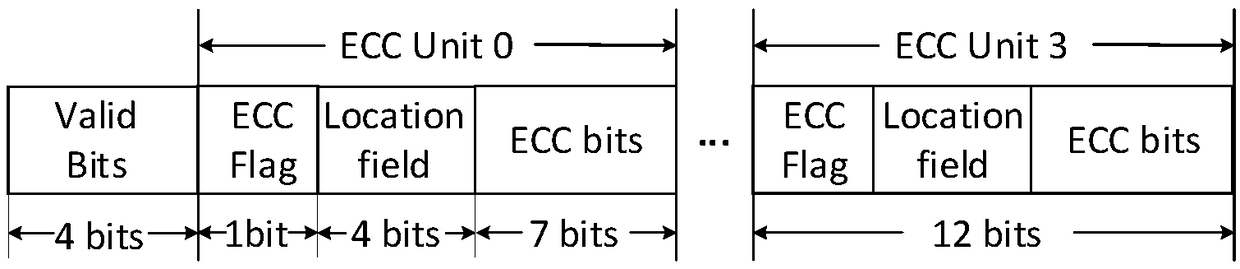

[0043] attached figure 1 It is a structure diagram of a detection and fault tolerance device for cache multi-bit hard errors under a near-threshold voltage according to the present invention. The whole device is composed of four parts: cache memory, BIST circuit, data compression module and data correction module. Wherein, the BIST circuit is used to detect the positions of hard errors in the cache memory and the memory of the device, the cache memory is composed of a Cache data memory and a Cache tag memory, and the data correction module includes an ECC memory, an error correction encoder and an error correction The decoder, data compression module includes an error map memory, a compression map memory, an empty sub-block detector, a sub-block compressor and a sub-block decompressor.

[0044] The thick line in the figure indicates the criti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com