MRAM chip

A chip and array technology, applied in the field of MRAM chips, can solve the problems of insufficient source line width, low power efficiency, and inability to provide, and achieve the effect of solving insufficient power supply, reducing energy consumption, and reducing the probability of continuous errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

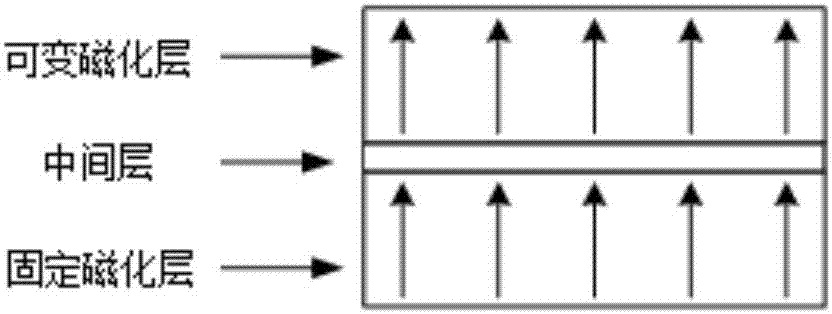

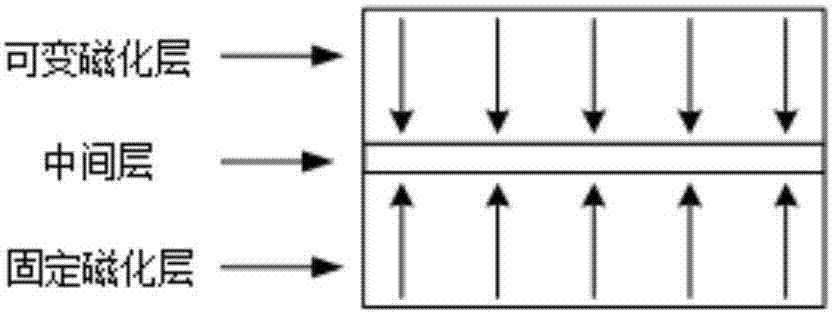

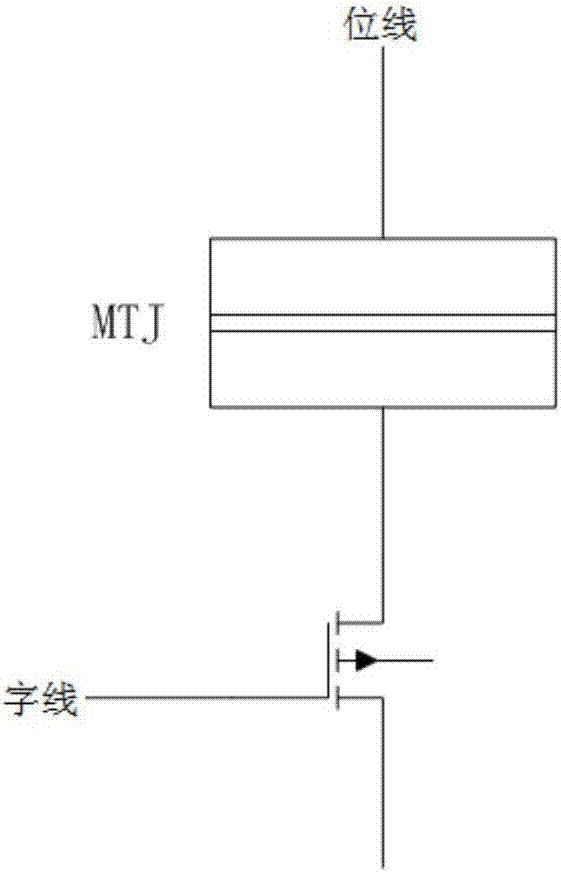

[0046] The MRAM chip of an embodiment of the present invention includes a plurality of arrays composed of MRAM memory cells, each array adopts a vertical layout of bit lines and source lines, and each bit in each word is stored in a different array respectively , each array stores one bit.

[0047] Because an array only writes one bit at a time, high voltage or negative voltage is no longer needed, so that the array design is simple and the energy consumption is reduced, and the problem of insufficient power supply of the source line is solved.

[0048] Each array includes a sense amplifier. Since an array only writes one bit at a time, all bit lines in the same row in the array share the sense amplifier, further reducing the cost of the MRAM chip.

[0049] Two adjacent rows in the array share a source line, such as Figure 7 As shown, the area occupied by the layout is further reduced, and the cost of the MRAM chip is reduced.

[0050] Each word can also include ECC error c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com