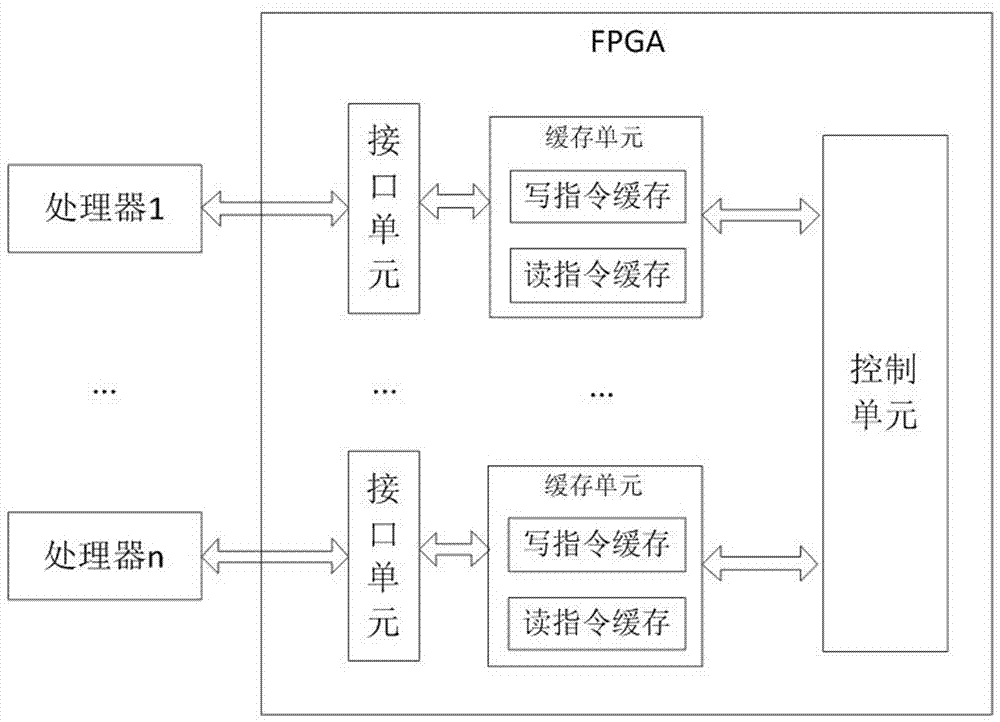

Communication system and communication method between multiple processors based on FPGA (Field Programmable Gate Array)

A communication system and processor technology, which is applied in the field of communication systems between multi-processors, can solve problems such as processor performance and cost waste, communication capacity limitations, processors that do not support Ethernet interfaces, etc., to reduce complexity, The effect of improving system stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

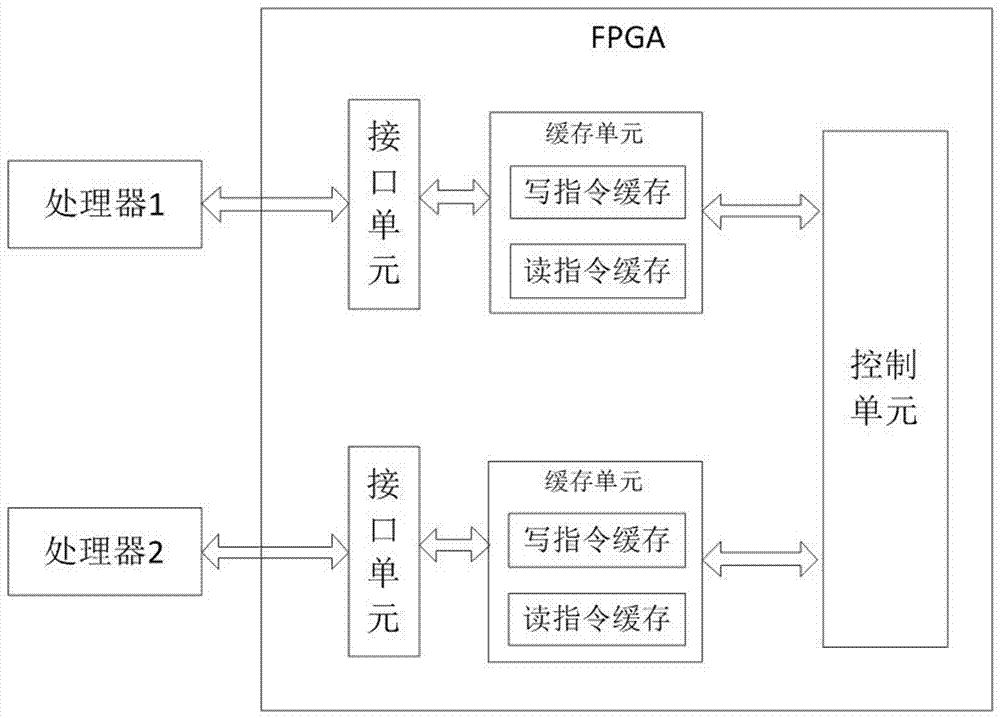

[0042] In this embodiment, communication between two processors is taken as an example, wherein the communication interface of processor 1 is a parallel bus interface, and the communication interface of processor 2 is an Ethernet interface.

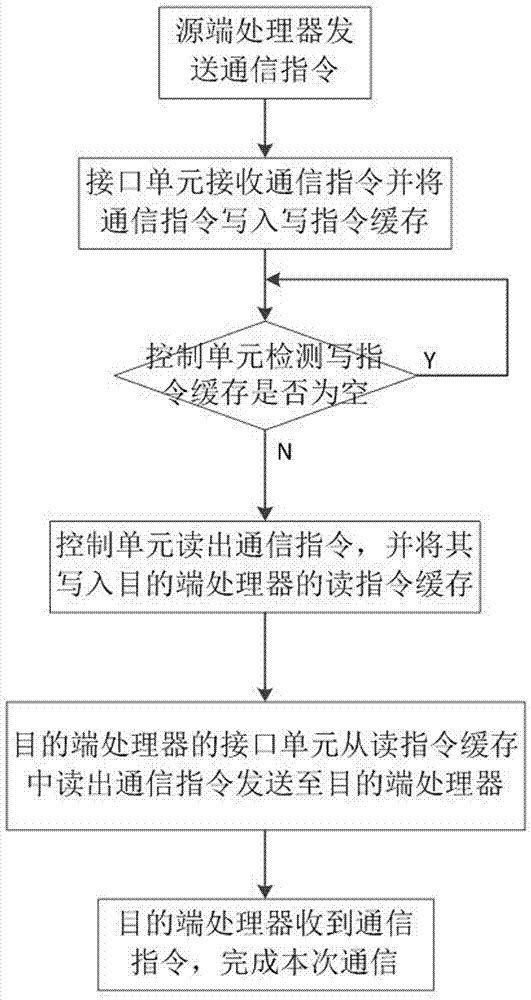

[0043] Firstly, the communication process in which processor 1 is the source processor and processor 2 is the destination processor is explained.

[0044] Step 1: Write communication commands

[0045] Processor 1 is interconnected with the interface unit through the parallel bus interface. Assuming that the data bus width in the parallel bus interface of processor 1 is 16 bits, that is, one write operation can write 2 bytes, then processor 1 divides a communication instruction into 4 write operations are written into the cache unit. After the interface unit detects the write operation of processor 1, it distinguishes which two bytes of the communication instruction the current write operation is based on the parallel bus interface address...

Embodiment 2

[0061] In this embodiment, communication between two processors is taken as an example, wherein the communication interface of processor 1 is an asynchronous RS232 interface, and the communication interface of processor 2 is an SPI interface.

[0062] First, the communication process in which processor 1 is the source processor and processor 2 is the destination processor is described.

[0063] Step 1: Write communication commands.

[0064] Processor 1 is interconnected with the interface unit through the asynchronous RS232 interface, refer to Image 6 It is the frame format of the asynchronous RS232 interface communication command. The frame starts with 0x55 bytes, followed by 8-byte communication commands, and ends with 0xAA bytes.

[0065] The processor 1 sends the communication instruction to the interface unit through the asynchronous RS232 interface according to the above frame format. The interface unit judges a complete frame according to the start identifier and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com