Scheduling method and device

A scheduling device and scheduling method technology, applied in the storage field, can solve problems such as poor configuration flexibility, low priority, no command or micro instruction sequence scheduling strategy adjustment, etc., achieve high configuration flexibility and improve scheduling efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

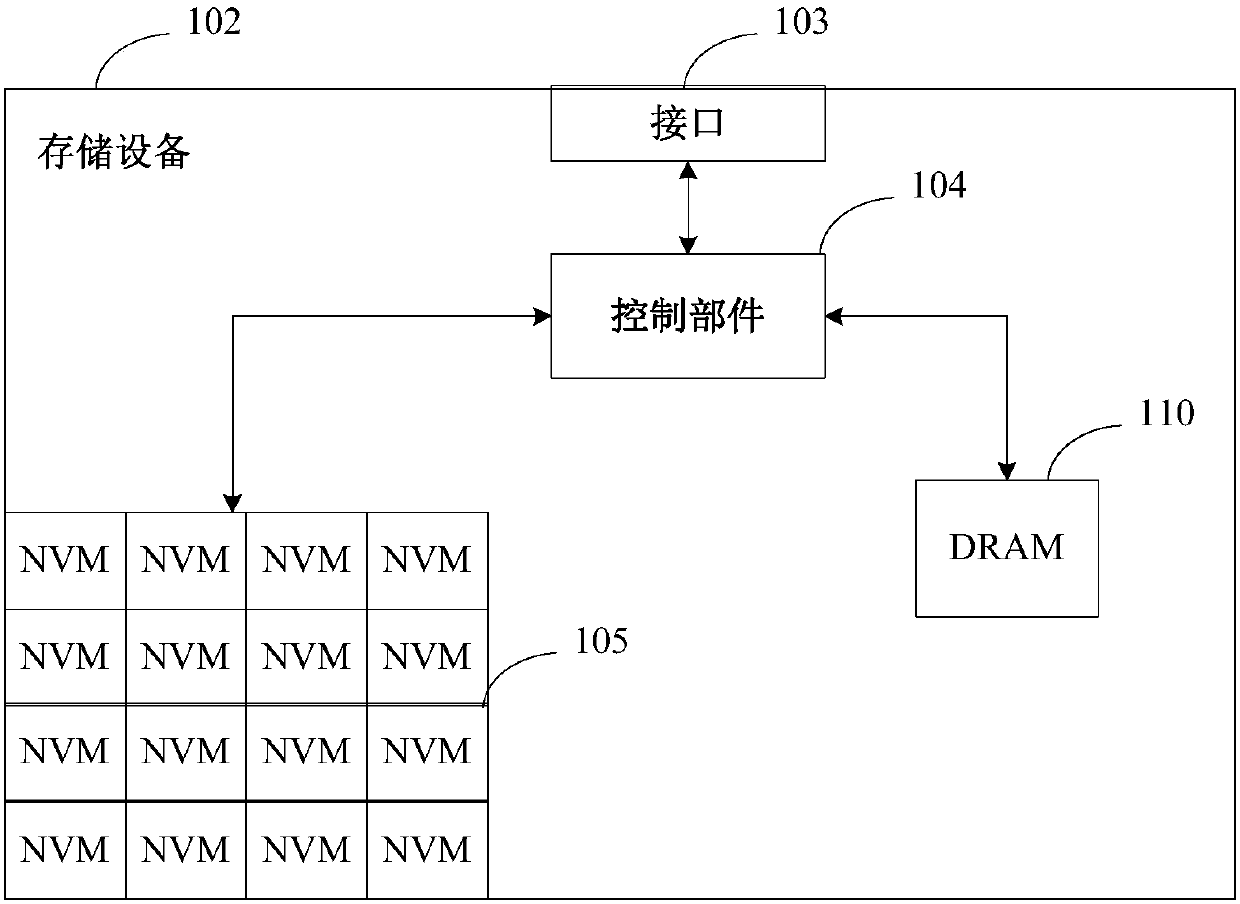

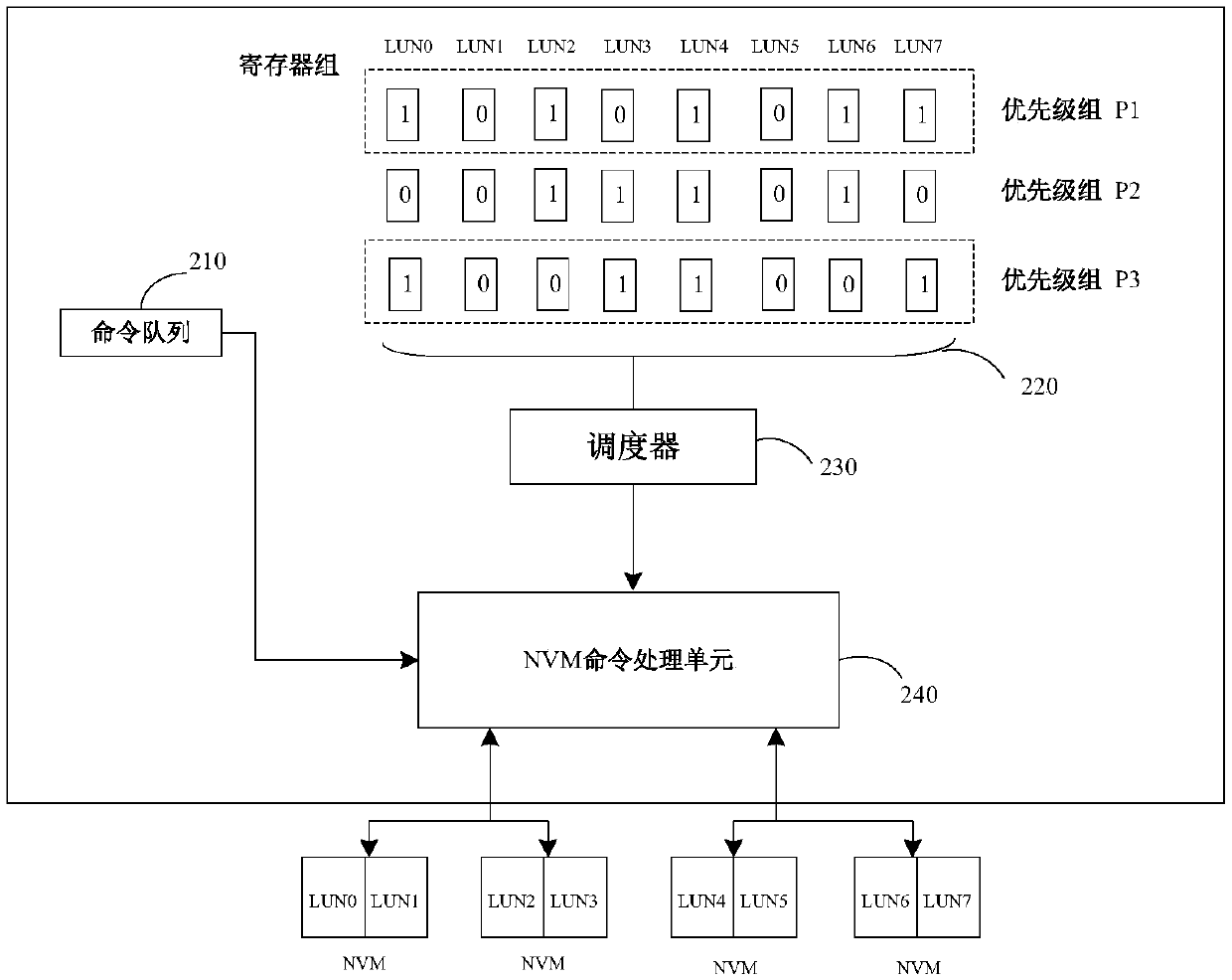

[0064] figure 2 is the control unit of the solid-state storage device according to Embodiment 1 of the present invention (see also figure 1 , a block diagram of the NVM interface controller of the control unit 104). The NVM interface controller includes a command queue 210 , a register set 220 , a scheduler 230 and an NVM command processing unit 240 .

[0065] The command queue 210 is used to receive commands from users or upper-level systems. Commands from the user or the upper system can include commands such as read, write, delete, and mark as invalid, and can also include commands such as reading the state of the NVM chip and reading / setting the NVM chip feature (feature). In addition, it can also include commands such as User-defined commands. The command queue 210 can be realized by a memory, a first-in-first-out memory, or a register file.

[0066] The NVM command processing unit 240 obtains commands from the command queue 210, and sends NVM interface commands conf...

Embodiment 2

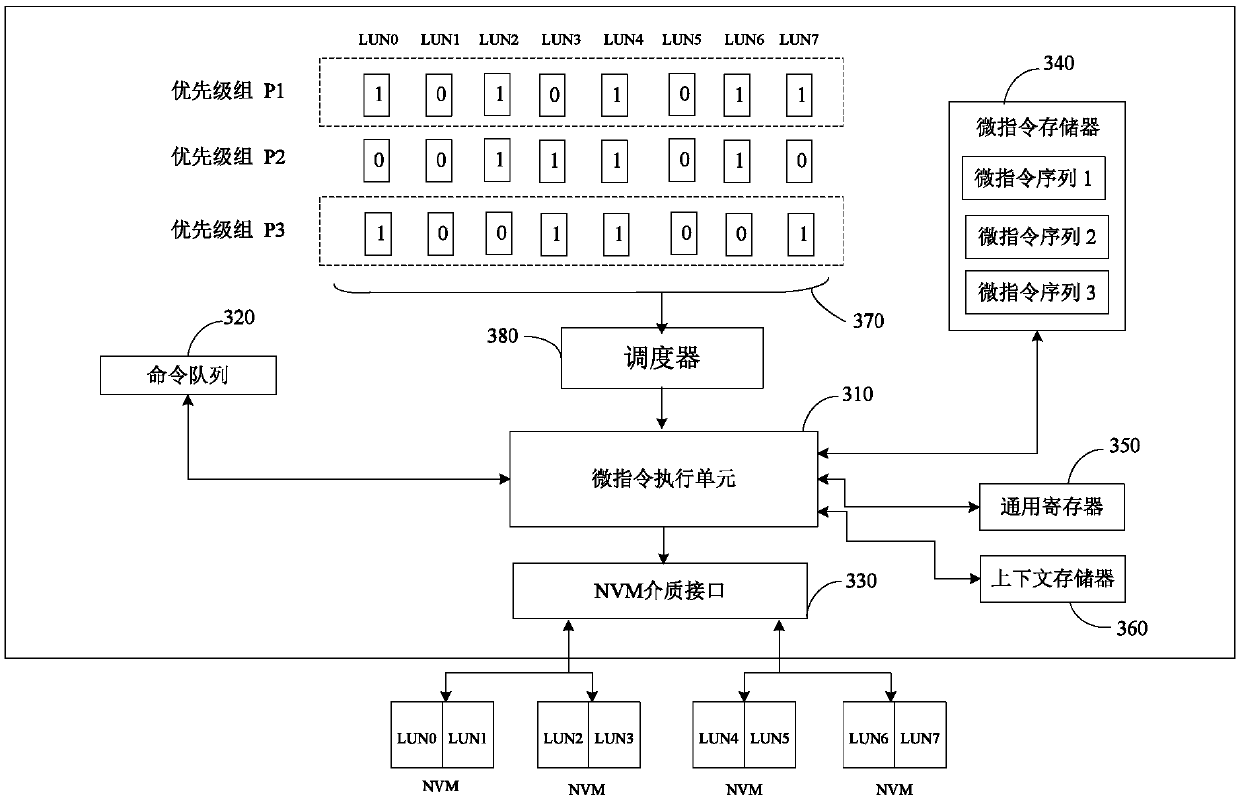

[0081] image 3 It is the control part of the solid-state storage device of Embodiment 2 of the present invention (see also figure 1 , a block diagram of the NVM interface controller of the control unit 104). The NVM interface controller generates commands to operate the NVM chip by processing microinstructions. To implement processing of microinstructions, the NVM interface controller includes a microinstruction execution unit 310 , a command queue 320 , an NVM media interface 330 , a microinstruction memory 340 , a context memory 360 and / or a general register 350 .

[0082] The microinstruction memory 340 is used for storing microinstructions. The microinstruction execution unit 310 reads and executes microinstructions from the microinstruction memory 340 . The microinstructions cause the microinstruction execution unit to issue commands to the NVM chip to operate the NVM chip through the NVM medium interface 330 . Exemplarily, the above commands include read, program, e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com