Heterogeneous multi-kernel power capping method through coordination of DVFS and task mapping

A technology of task mapping and nuclear power, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve problems such as system power consumption and unbalanced load, so as to improve system performance and ensure system performance , The effect of improving system performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with the accompanying drawings.

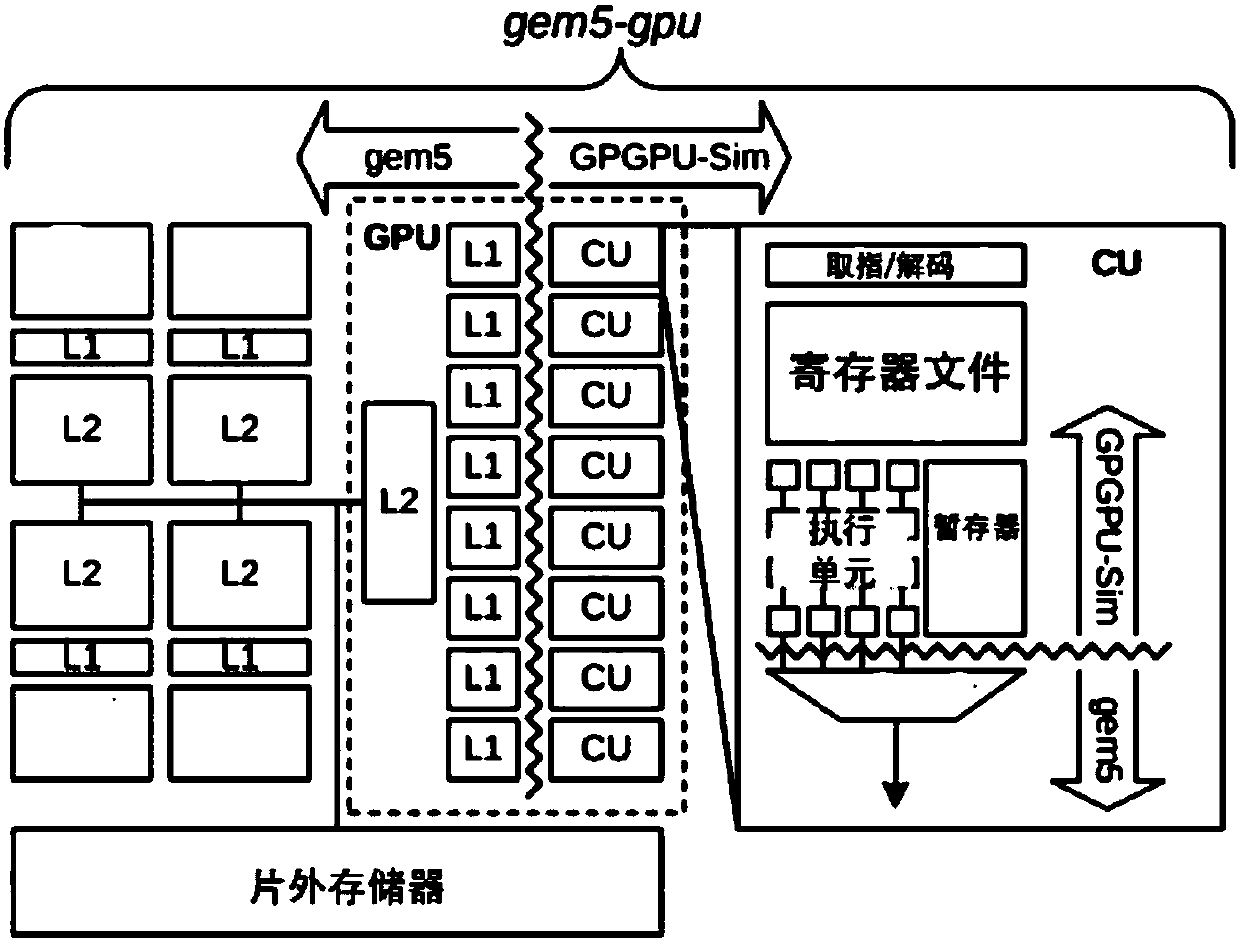

[0043] figure 1 It is a heterogeneous multi-core system built by the gem5-gpu simulator. It simulates a heterogeneous architecture that integrates a 4-core CPU and a GPU composed of 8 CUs on the same chip. In gem5-gpu, you can Modify the simulation architecture flexibly according to the configuration file, and gem5-gpu supports DVFS.

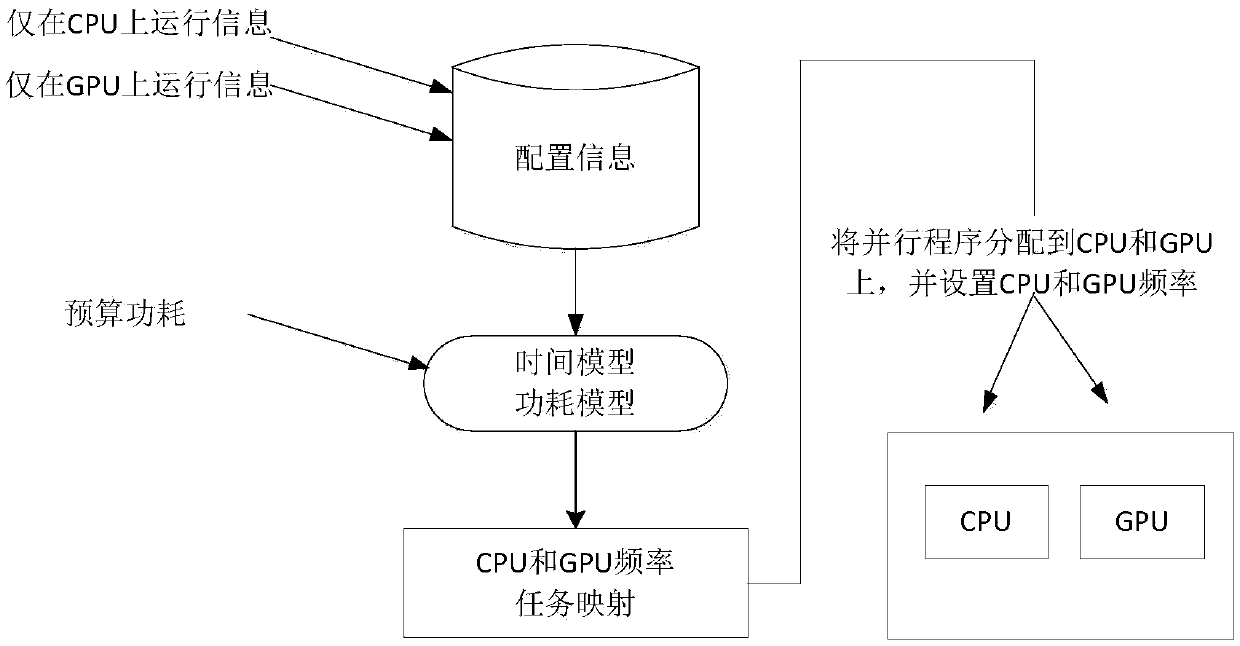

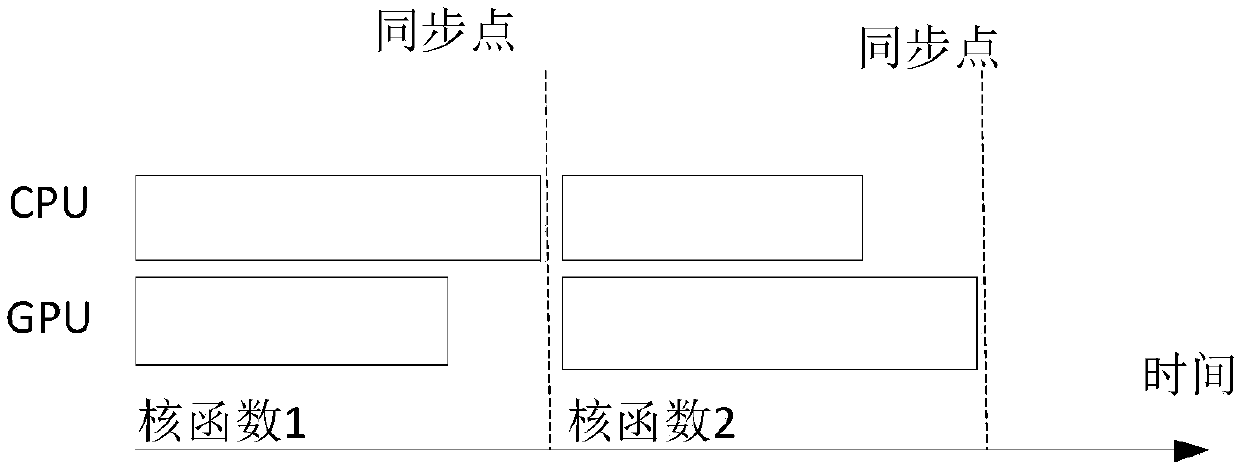

[0044] In the heterogeneous multi-core system constructed by gem5-gpu simulation, the present invention realizes a power capping method by combining DVFS and task mapping, including the following specific steps:

[0045] Step 1, implement measuring the total computing node time, CPU power consumption and GPU power consumption after the execution of the application program is completed.

[0046] In gem5-gpu, after an application is executed, a file stat.txt containing all program execution information will be automatically generated, in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com