tsv plating method

A technology of electroplating solution and current value, applied in circuits, semiconductor devices, etc., can solve problems such as the influence of rewiring process semiconductor device production

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

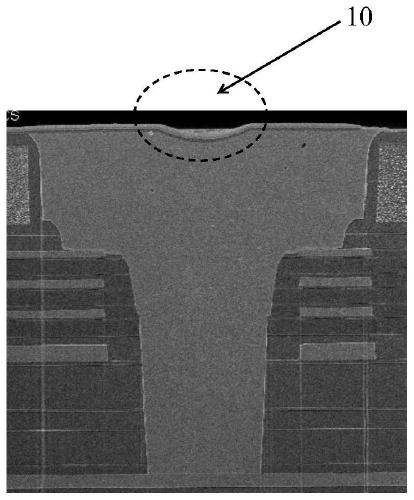

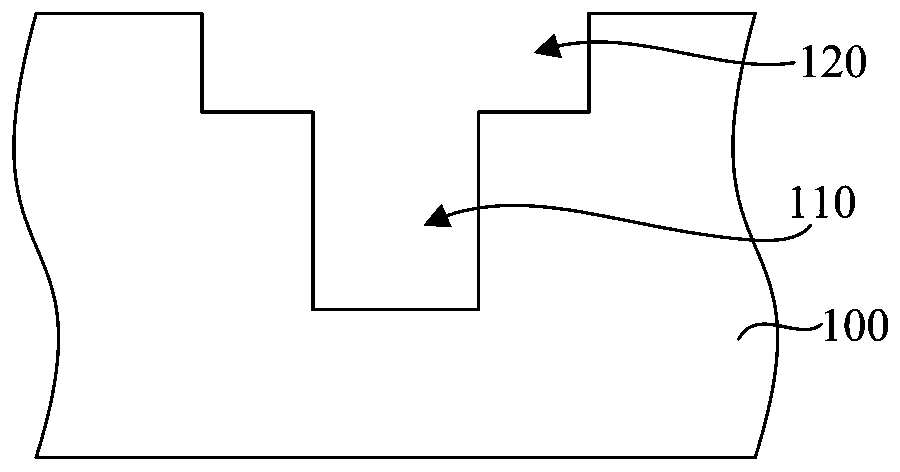

[0030] At present, in the TSV process of integrated circuits, it is usually necessary to fill small-sized TSVs (bottom pore diameters of about 20-100 nm), large-sized TSVs (bottom pore diameters greater than 1 μm) and trenches above TSVs. The filler metal is copper (Cu). However, the applicant found that using the current TSV electroplating method, especially for large-sized TSVs, pits are formed on the surface of the TSV structure after electroplating. After measurement, the depth of the pits is even It will reach 6-10μm, so it cannot be removed even if the subsequent CMP process is performed, such as figure 1 The pit 10 in is the pit that still remains after the CMP process. The existence of the pits 10 will affect the flatness of the silicon substrate, and will affect the subsequent redistribution layer (Redistribution Layer, RDL) layer and the fabrication of semiconductor devices.

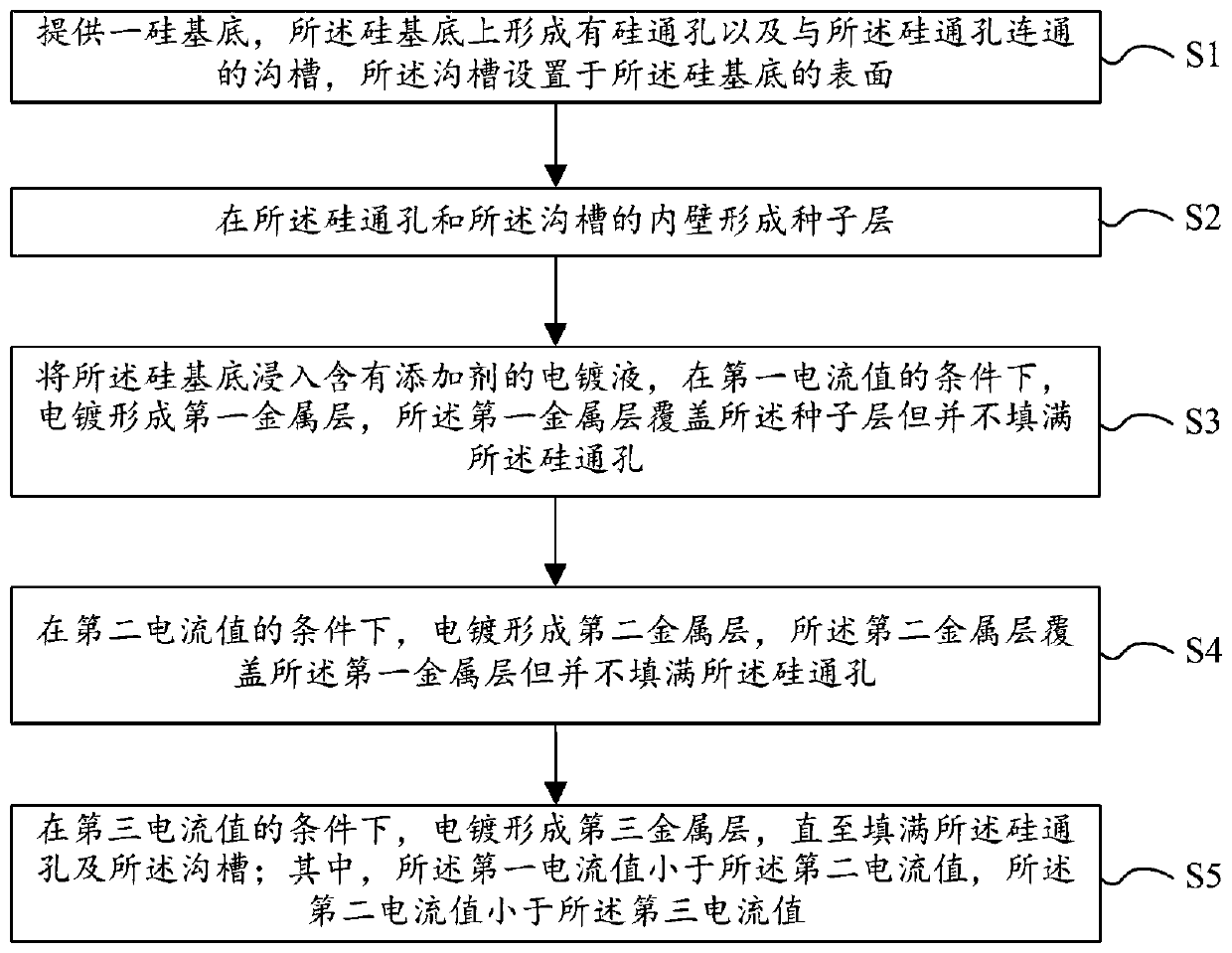

[0031] This embodiment provides a TSV electroplating method, which divides the electropla...

PUM

| Property | Measurement | Unit |

|---|---|---|

| pore size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com