Integrated chip crack detection device and method

A crack detection and integrated chip technology, applied in measurement devices, optical testing flaws/defects, instruments, etc., can solve the problems of inappropriate metal materials, inappropriate non-conductive materials, limited application value, etc., to improve reliability and reliability. Safety, improved spatial resolution, effect of eliminating noise components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

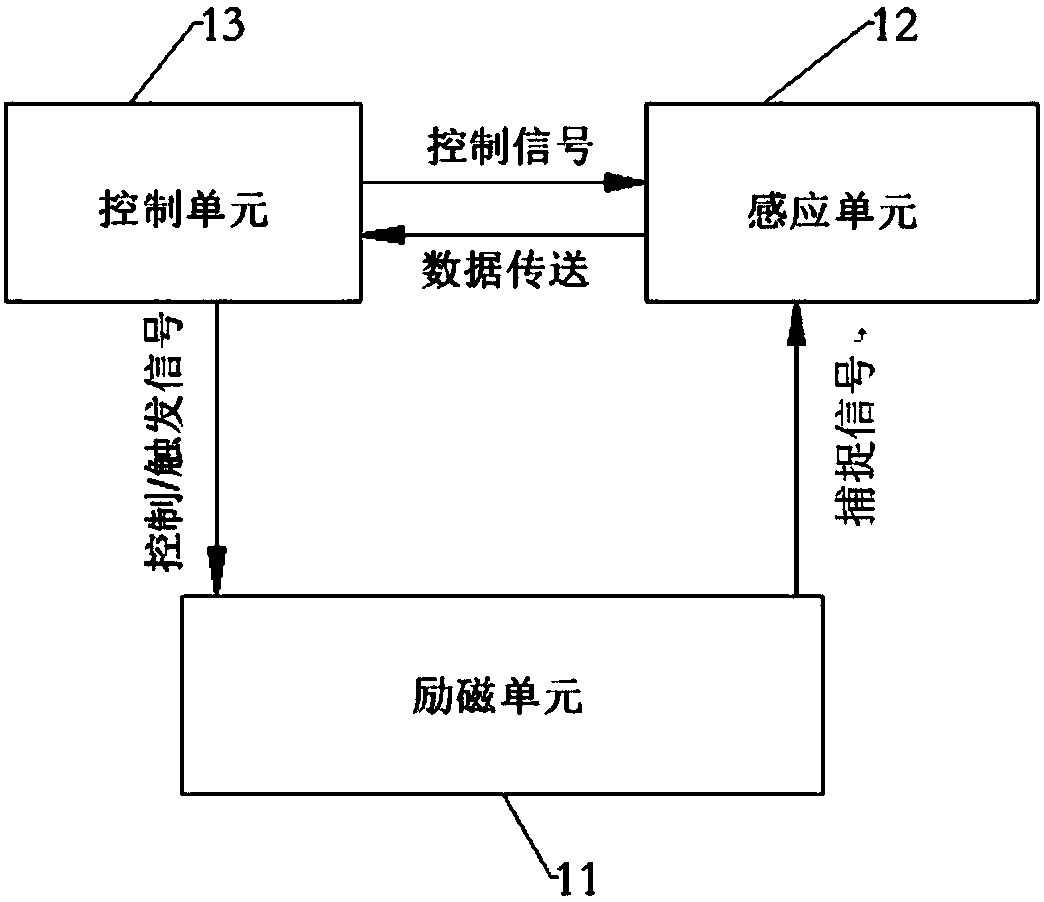

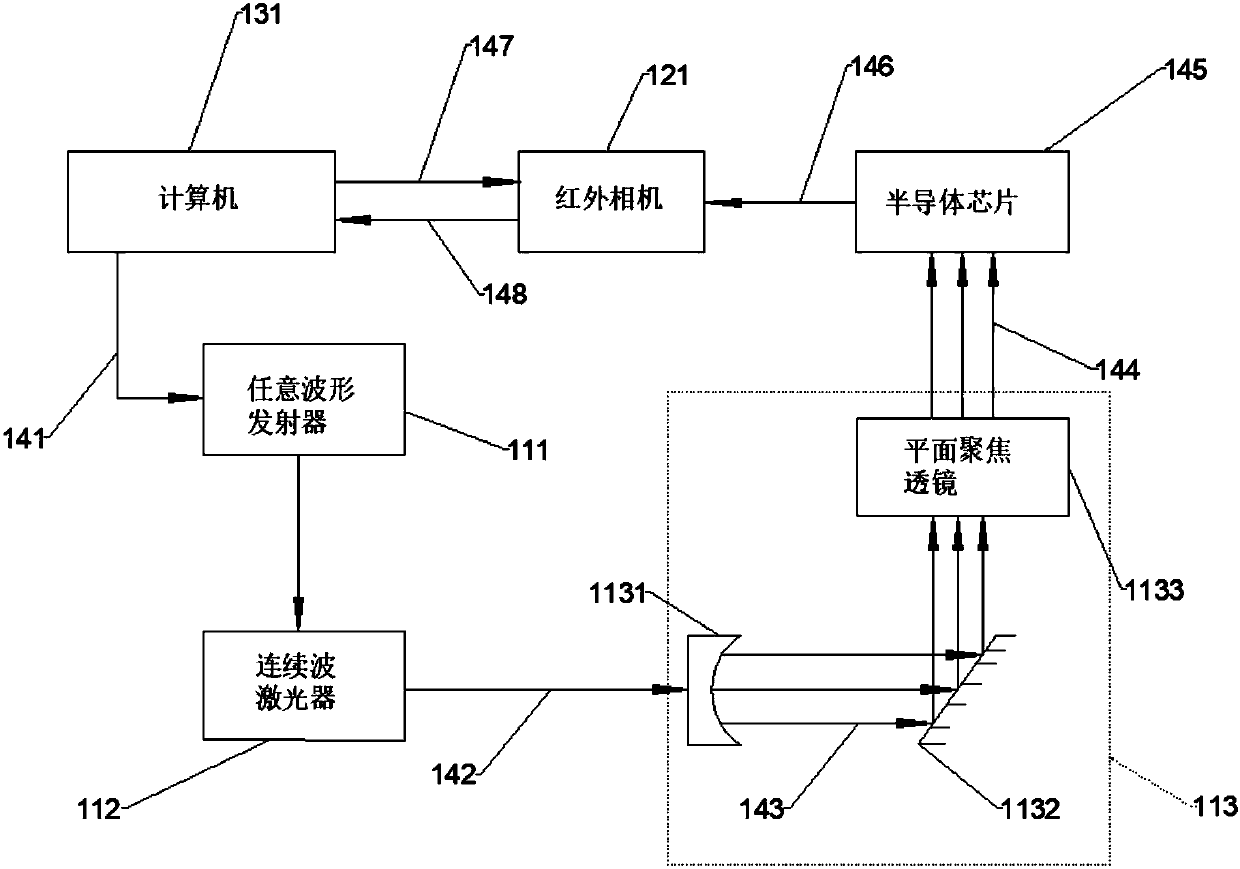

[0047] The integrated chip crack detection device of the present invention is based on the new line laser lock-in thermal imaging technology, which can achieve the following technological breakthroughs: (1) completely non-contact, non-damaging and non-invasive during detection; (2) not only can detect conductive materials, but also Applied to non-conductive materials; (3) Realize a self-developed visualization algorithm for chip cracks without baselines with intellectual property rights. Baseline-free crack diagnosis only requires thermal images of the current state and does not require any thermal images of historical states. The detection efficiency is high and it is suitable for online detection ; (4) The capability of crack detection is improved by improving the spatial resolution of the thermal image and eliminati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com