Double patterning method

A double patterning and planarization technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of poor target graphics quality, affecting the performance and yield of semiconductor structures, etc., to achieve small surface height difference and improve quality effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be known from the background art that, in the prior art, the double patterning method is used to etch the substrate, and the quality of the pattern formed in the etched substrate is poor.

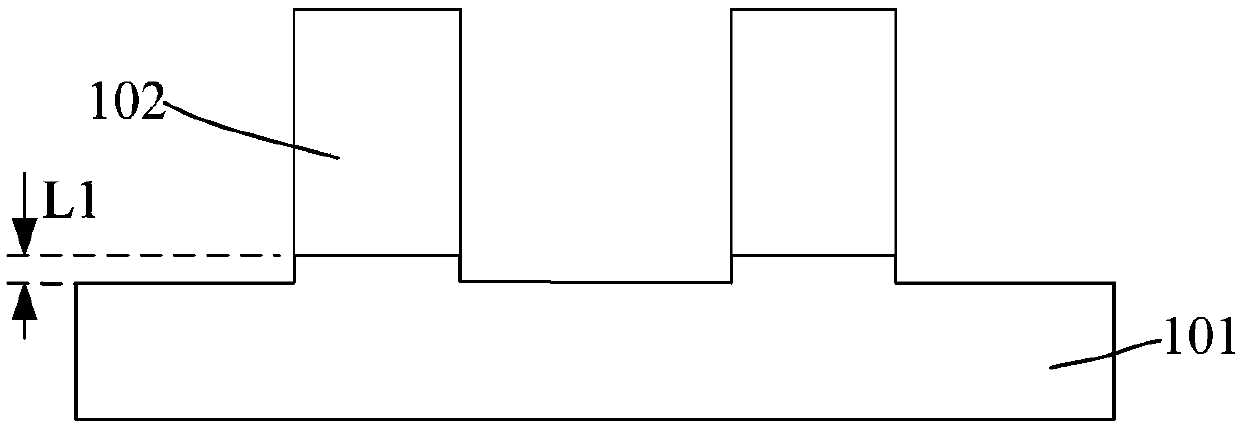

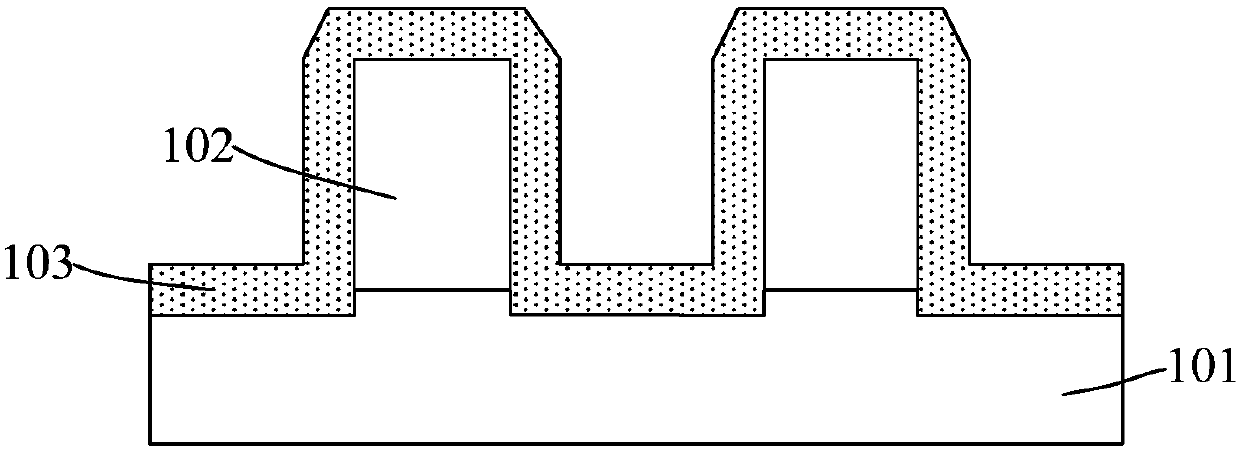

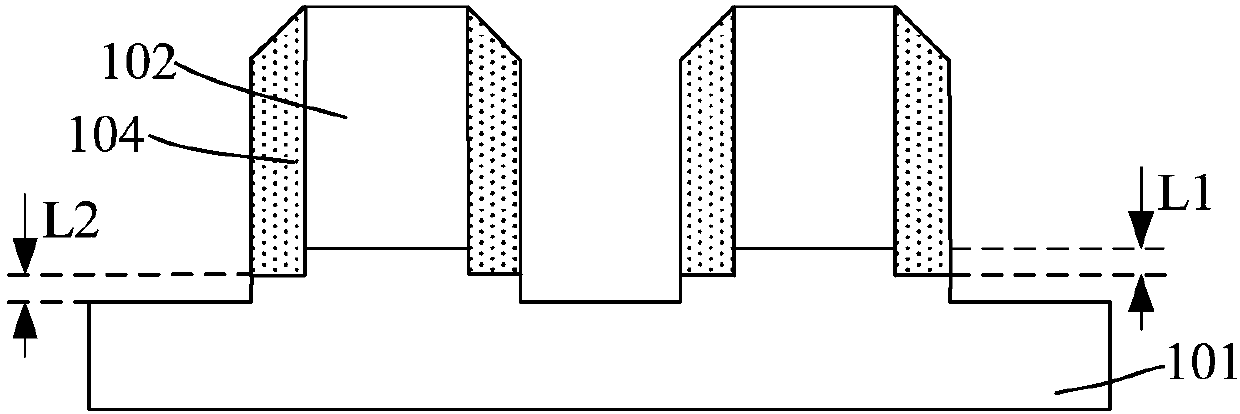

[0033] Figure 1 to Figure 5 It is a schematic cross-sectional structure diagram of the process of forming a semiconductor structure using a double patterning method.

[0034] reference figure 1 , A substrate 101 is provided, and a plurality of discrete core layers 102 are formed on the surface of the substrate 101.

[0035] Moreover, the process of forming the core layer 102 is likely to cause over etch to the substrate 101, so that the top surface of the substrate 101 under the core layer 102 is higher than the top surface of the substrate 101 exposed by the core layer 102, and the top surface of the substrate 101 under the core layer 102 The minimum distance between the top of the substrate 101 and the top of the substrate 101 exposed by the core layer 102 is L1.

[0036] reference...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com