NoC (Network on Chip) error detection correction retransmission fault-tolerant method based on dual modular redundancy

A dual-mode redundancy, error correction and detection technology, applied in the direction of error prevention, transmission system, digital transmission system, etc., can solve the problem that transmission delay, power consumption, effective data throughput cannot be taken into account at the same time, and Baotou microchips are not specially protected , error transmission and other issues, to achieve the effect of improving power consumption, improving link utilization, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described below in conjunction with the accompanying drawings.

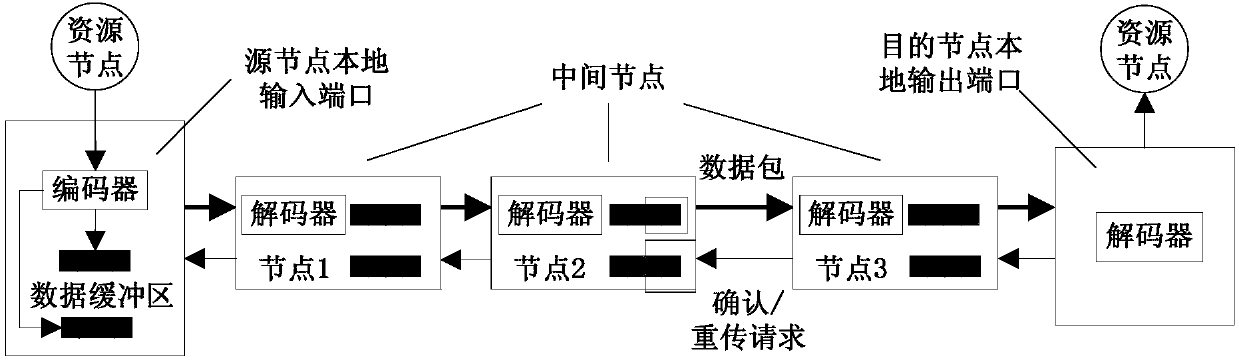

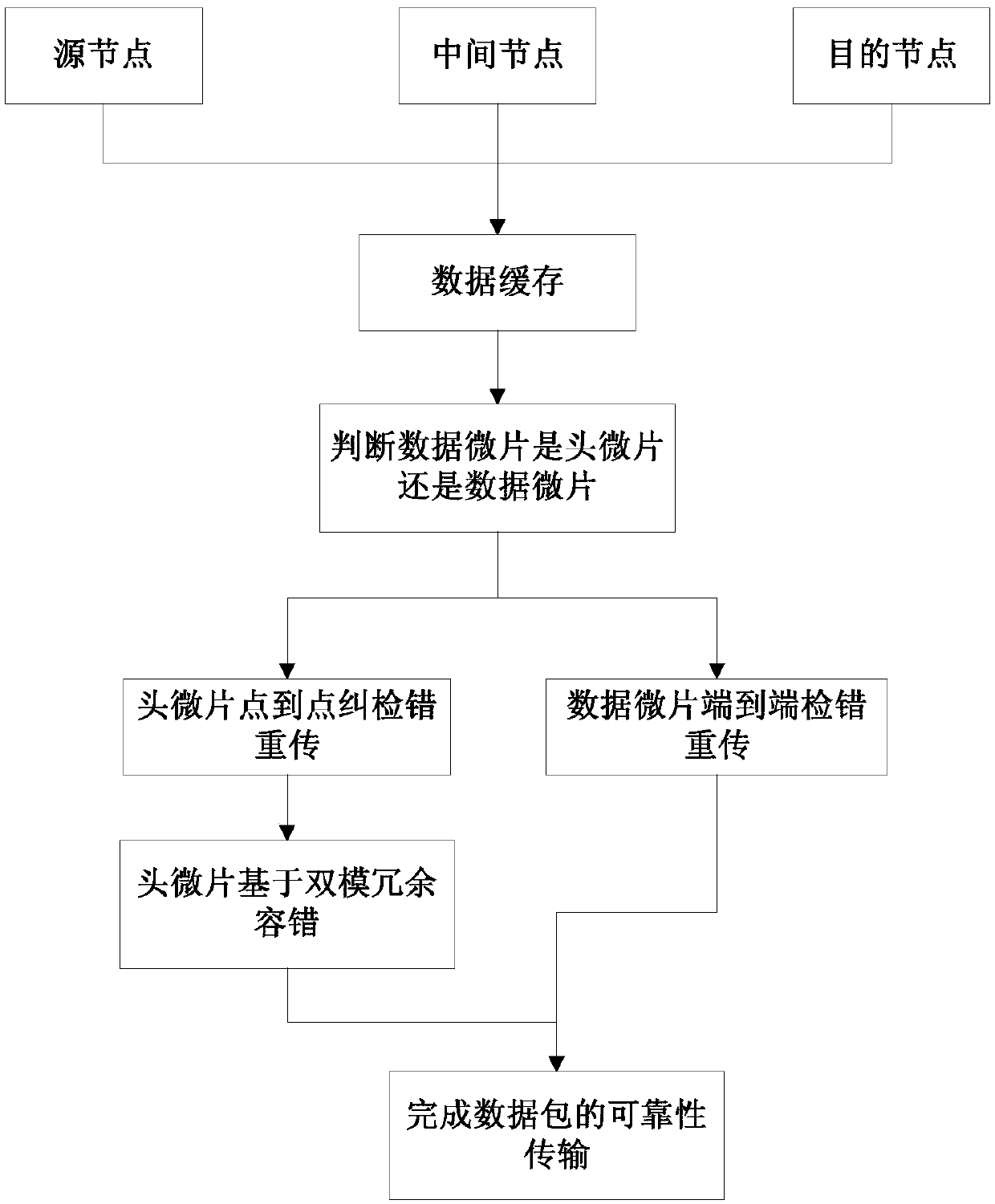

[0036] like figure 1 As shown, the error-correcting-detection-retransmission fault-tolerant method model of the present invention requires that the processing of the data packet at the source node, the intermediate node, and the destination node cooperate with each other to complete the transmission of the entire data packet. The source node sends the data packet to the destination node, and the intermediate node performs dual-mode redundant retransmission fault tolerance and data forwarding on the header microchip.

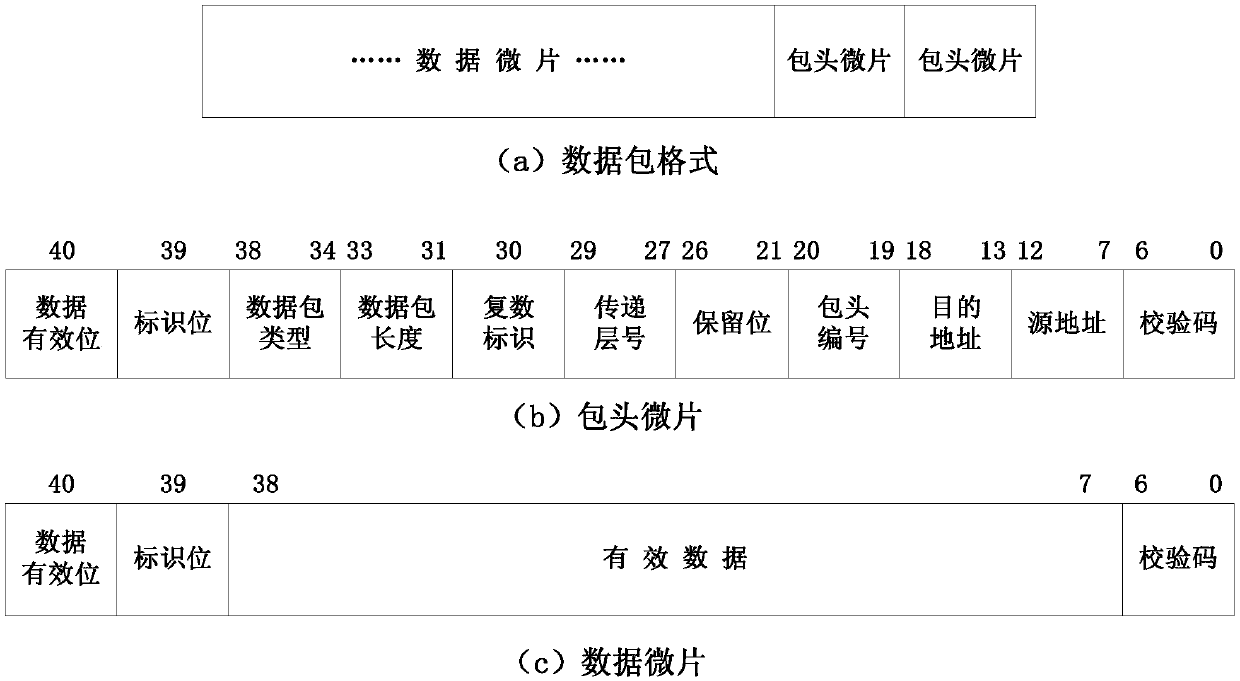

[0037] like image 3 Shown is the structural diagram of the transmission data packet in the present invention. Wherein (a) is the format of the data packet, (b) is the format of the packet header flake, and (c) is the format of the data flake. Each data packet contains two identical header flakes and multiple data flits, and the data bit width of the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com