Storage, forming method thereof and semiconductor device

A memory and conductor technology, applied in the field of memory and its formation, semiconductor devices, can solve problems such as position deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

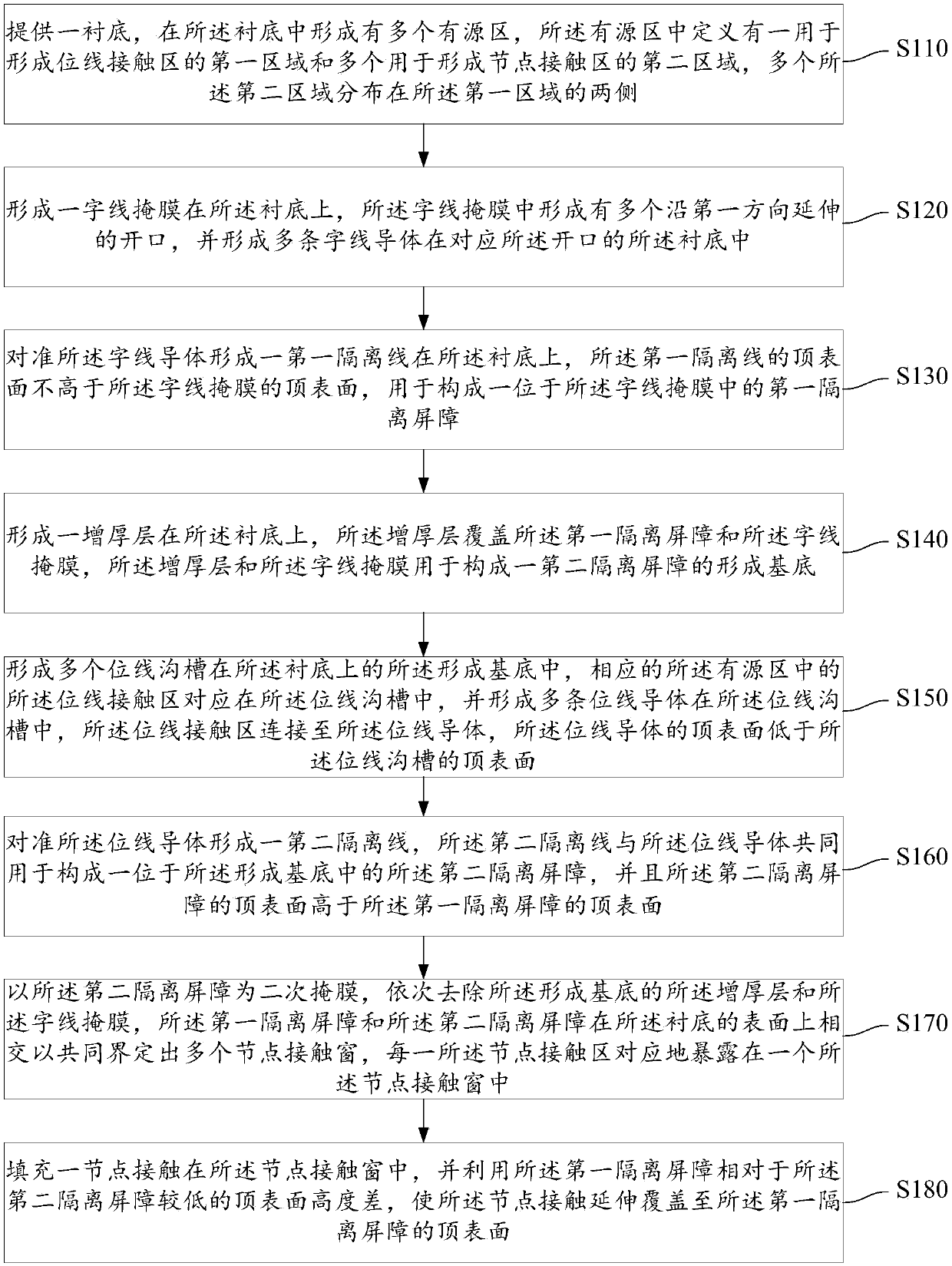

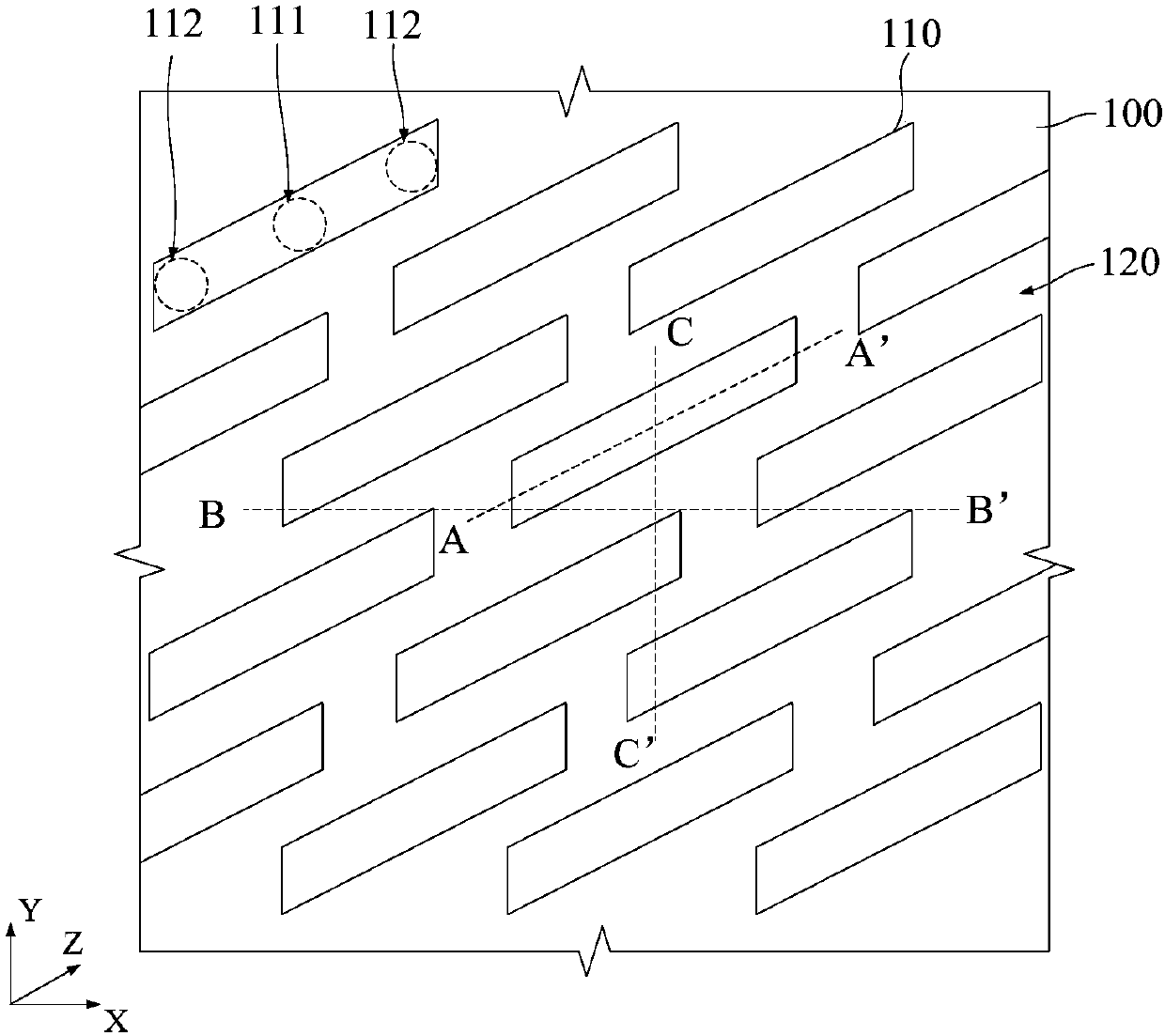

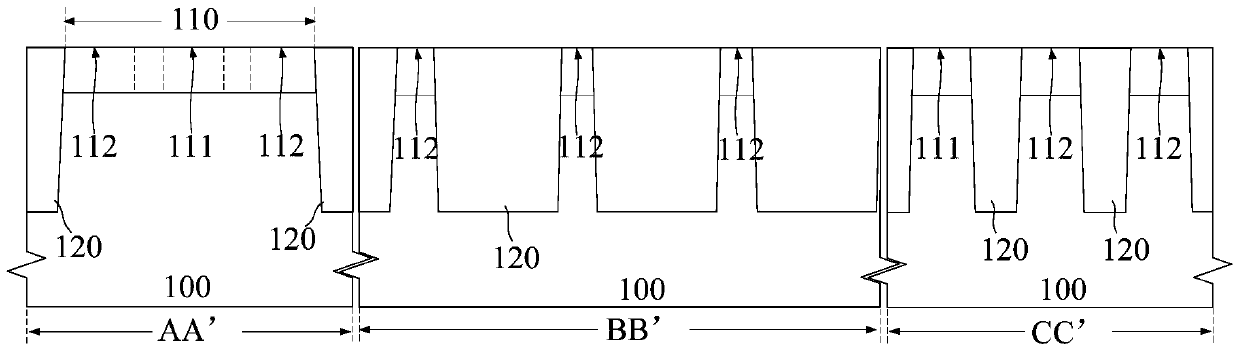

[0116] Figure 2a is a top view of the memory forming method in Embodiment 1 of the present invention when step S110 is executed, Figure 2b for Figure 2a The shown cross-sectional views of the memory forming method in Embodiment 1 of the present invention along the directions AA', BB' and CC when step S110 is executed.

[0117] In step S110, refer to Figure 2a with Figure 2b As shown, a substrate 100 is provided, and a plurality of active regions 110 are formed in the substrate 100, and a first region for forming a bit line contact region 111 and a plurality of active regions 110 are defined in the active region 110. For forming the second region of the node contact region 112 , a plurality of the second regions are distributed on both sides of the first region.

[0118] In this embodiment, the active region 110 extends obliquely relative to the first direction (Y direction), and a plurality of the first regions extend in the extending direction of the active region 11...

Embodiment 2

[0185] Another object of the present invention is to provide a memory, which utilizes a plurality of first isolation barriers and a plurality of second isolation barriers to define node contact windows corresponding to node contact regions, and the second isolation barrier utilizes A second isolation line makes the top surface of the second isolation barrier higher than the top surface of the first isolation barrier, so that a node contact extending along the extension direction of the second isolation barrier can be formed.

[0186] Figure 12ais a top view of the memory in Embodiment 2 of the present invention, Figure 12b for Figure 12a The shown cross-sectional views of the memory in Embodiment 2 of the present invention along the directions AA', BB' and CC. combine Figure 12a with Figure 12b As shown, the memory includes:

[0187] A substrate 100, a plurality of active regions 110 are formed in the substrate 100, a bit line contact region 111 and a plurality of no...

Embodiment 3

[0200] Based on the memory and its forming method described above, the present invention also provides a semiconductor device. The semiconductor device includes:

[0201] a substrate in which a plurality of first contact regions are formed;

[0202] a plurality of first isolation barriers, formed by a plurality of first isolation lines formed on the substrate, and extending in a first direction;

[0203] a plurality of second isolation barriers formed on the substrate and extending along a second direction, the first isolation barriers and the second isolation barriers intersecting on the surface of the substrate to jointly define a plurality of A contact window, each of the first contact regions corresponds to one of the contact windows, and the second isolation barrier includes a second isolation line, so as to use the second isolation line relative to the first isolation line in the a thickness difference on the substrate such that the top surface of the second isolation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com