System of verification and solution of satisfiability modulo theory (SMT)-based fault tree and method thereof

A technology of fault tree and modulus theory, which is applied in the field of fault tree verification and solution system, can solve problems such as no effective method, no effective and convenient method to ensure the correctness of fault tree, permutation and combination explosion, etc., to ensure correctness , avoid approximation error, and ensure the effect of correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

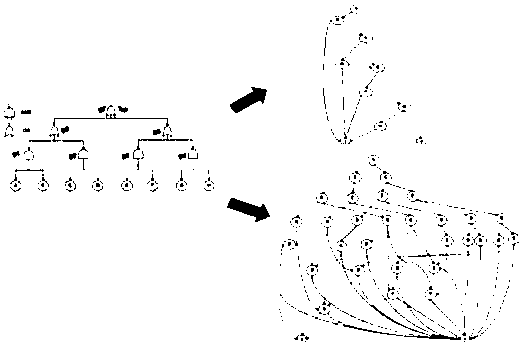

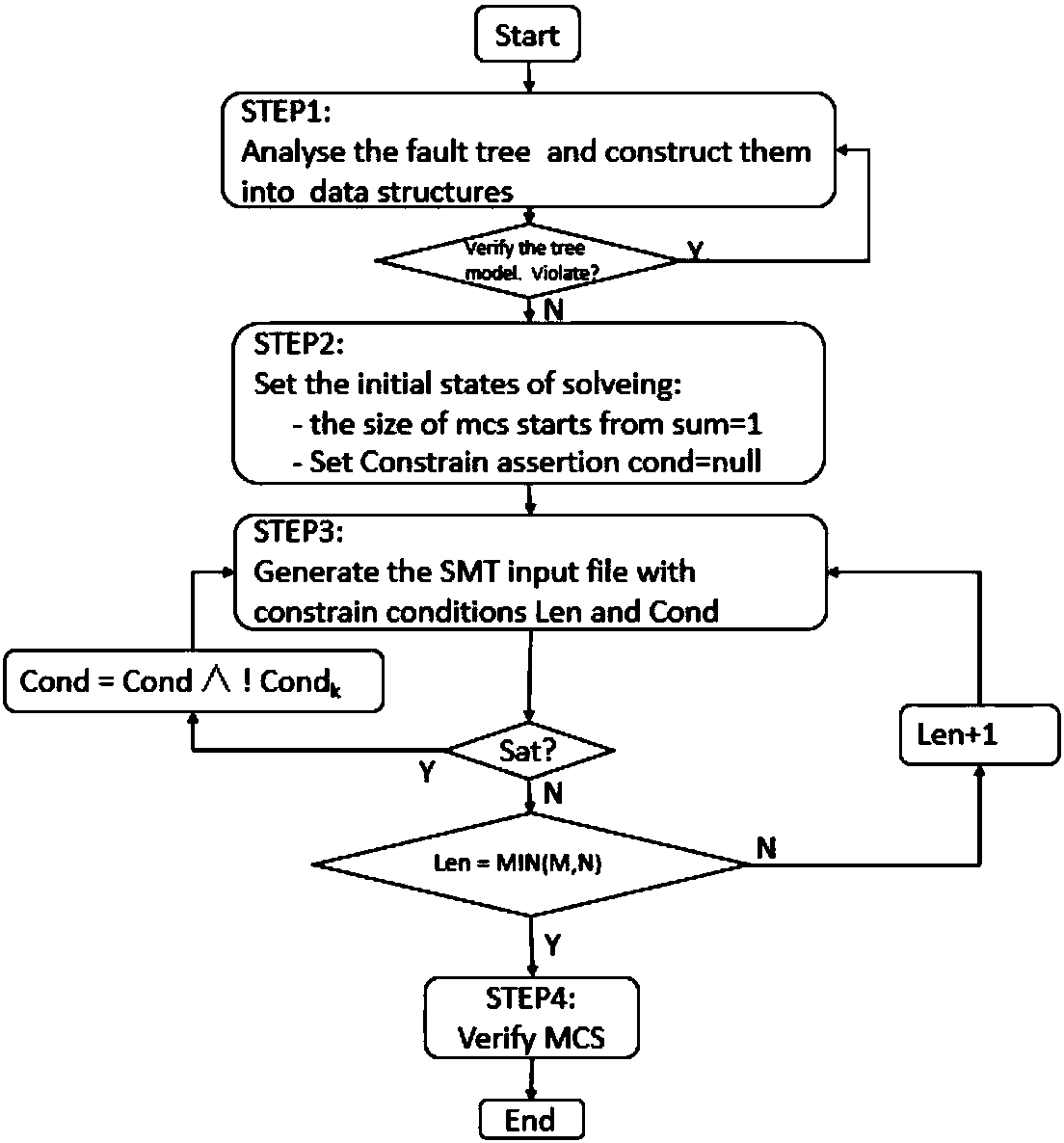

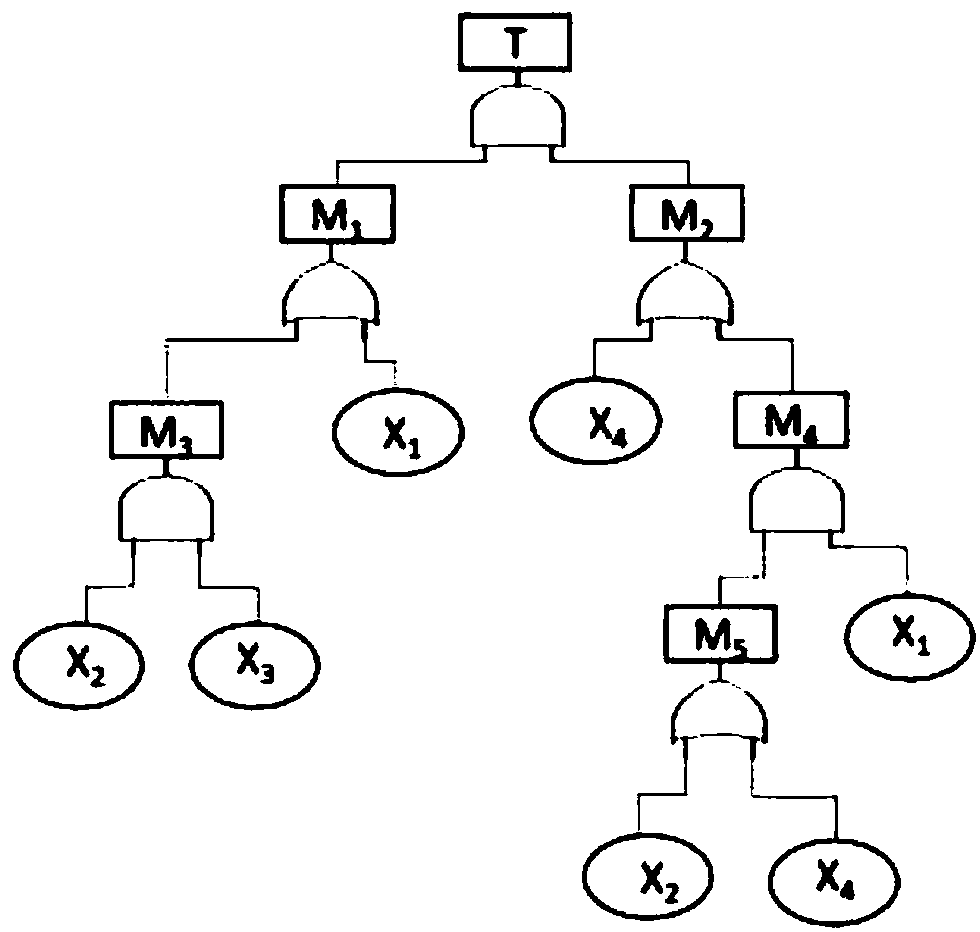

[0026] Such as Figure 1-5As shown, the verification and solution system of the fault tree based on the satisfiable modulus theory includes the fault tree described in the formal language of the satisfiable modulus theory, that is, the relationship between the nodes of the fault tree is analyzed and the logical relationship is described. The description process includes the The logical relationship between nodes is defined, and the specification of the satisfiable module theory is described according to the formal language. The specific technology includes the SMT formal language, but not limited to the current SMT language. Including the formal verification tool, that is, the SMT solver, to receive and verify the formal logic formula of the input fault tree, check its correctness, and give an error report. The user modifies the fault tree to meet the correctness requirements. The verification process includes: receiving The input file of the fault tree and its logical relatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com