Method for quickly obtaining node simulation state in digital gate level circuit

A technology of gate-level circuits and internal nodes, which is applied in the field of quickly obtaining the simulation state of internal nodes of digital gate-level circuits, which can solve the problems of long time consumption, complexity, and inconvenient gate-level circuits, so as to improve accuracy and reduce complexity , the effect of reducing the simulation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

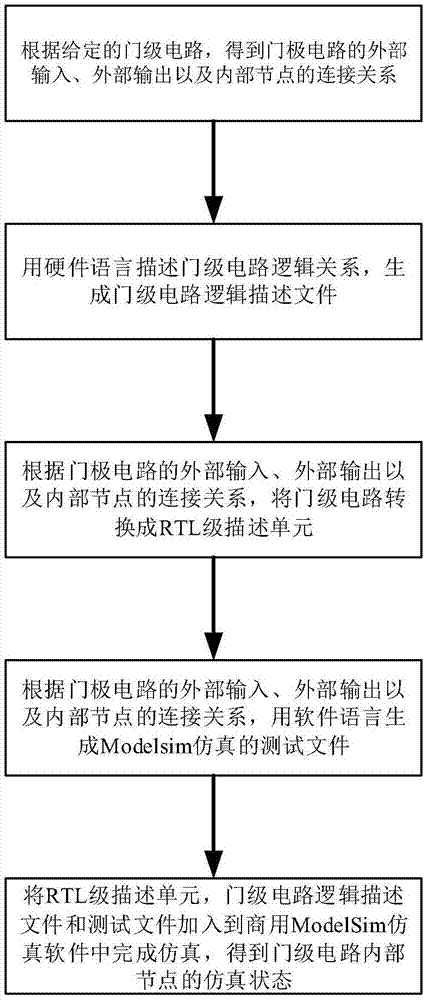

[0022] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0023] Refer to attached figure 1 , the gate-level circuit targeted by the present invention includes 4 external input terminals G0, G1, G2, G3, 6 D flip-flops DFF nodes DFFG4, DFFG5, DFFG6, DFFG7, DFFG8, DFFG9, 3 NOT gates NOT nodes NOTG15, NOTG16, NOTG20, 1 AND node ANDG19, 2 OR nodes ORG17, ORG18, 4 NOR nodes NORG11, NORG12, NORG13, NORG14, 1 NAND node NANDG10 and 2 external outputs G21 , G22.

[0024] Refer to attached figure 2 , the present invention is based on the key node extraction method of gate-level circuit simulation, comprises the following steps:

[0025] Step 1: According to figure 1 Given a gate-level circuit, the connection relationship between the external input, external output and internal nodes of the gate circuit is obtain...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com