Wafer test method for memory chip with redundant cell

A memory chip and memory testing technology, which is applied to static memory and instruments, can solve the problems of long test time, high test cost, and low test efficiency, etc., to improve test efficiency, reduce test cost, and reduce reading time Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Firstly, the test mechanism of the existing memory tester to test chips with redundant functions is explained as follows:

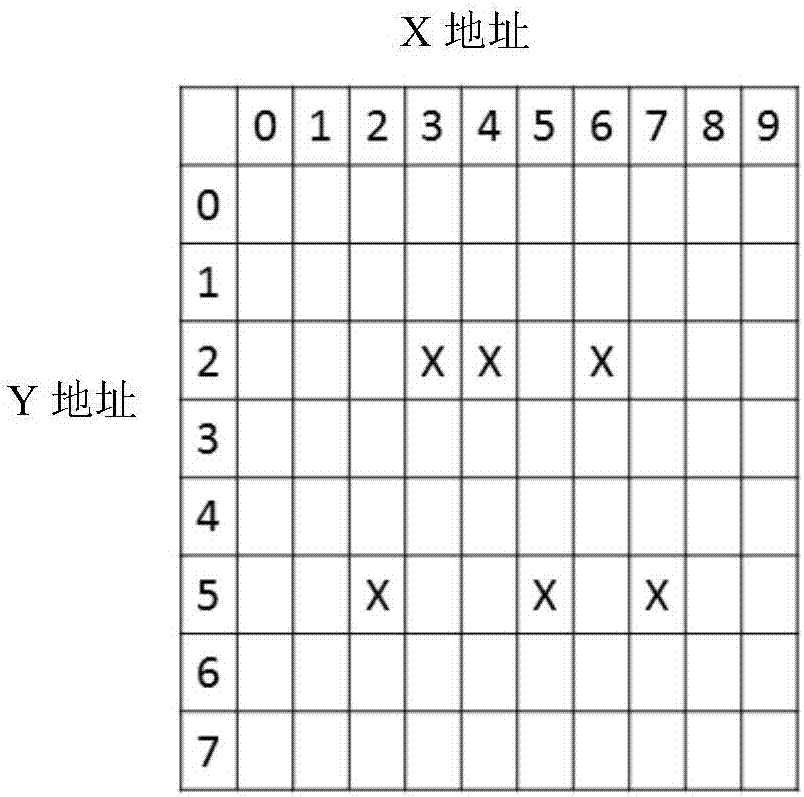

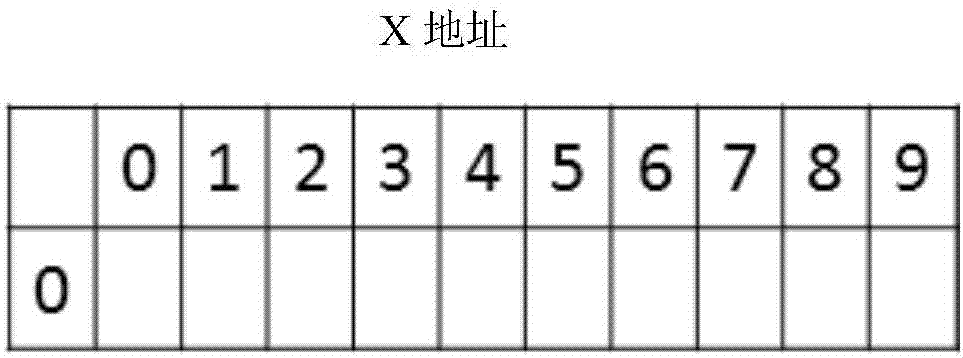

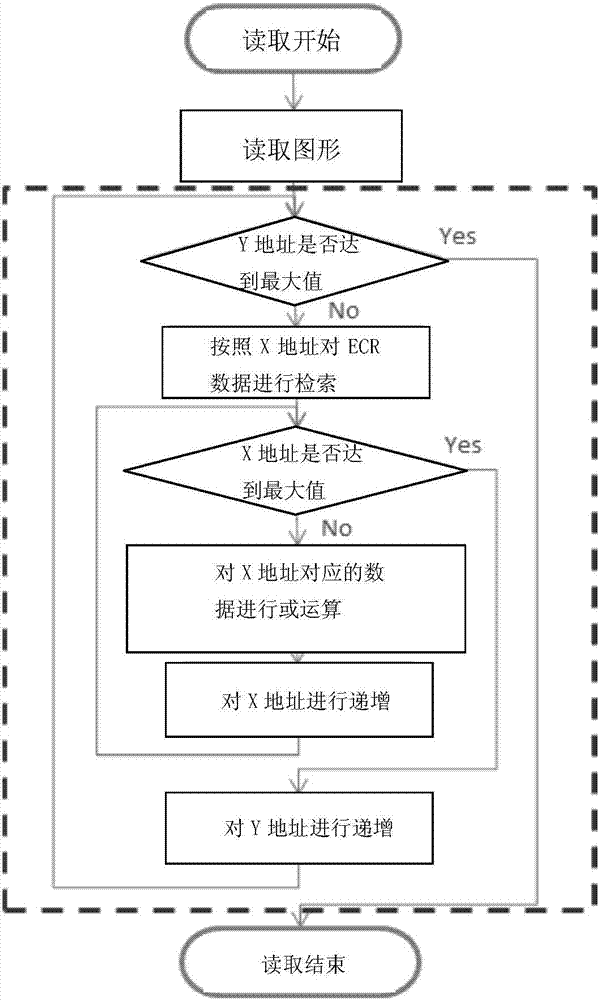

[0032] To test this type of chip, a dedicated memory tester is generally required, because the memory tester has a special RAM to store the address of the failed unit of the chip under test (DUT), generally referred to as ECR or AFM. For a simple example, such as figure 1 As shown, it is the array structure diagram of the main area of the memory chip on the wafer. A certain memory chip is composed of 10 units of X address and 8 units of Y address. X address is defined as column address, and Y is defined as row address; while redundant The unit unit is one line, that is, 10 units in the X direction and 1 unit in the Y direction. For the structure diagram of redundant units, please refer to figure 2 shown. Because the smallest unit of a redundant unit is a row, as long as there is a unit failure in a row, this row is judged to be a failure and n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com