Flip chip type semiconductor packaging structure

A packaging structure, flip-chip technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as bump cracks, packaging failure, failure, etc., to improve thermo-mechanical reliability. , the effect of dispersion distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

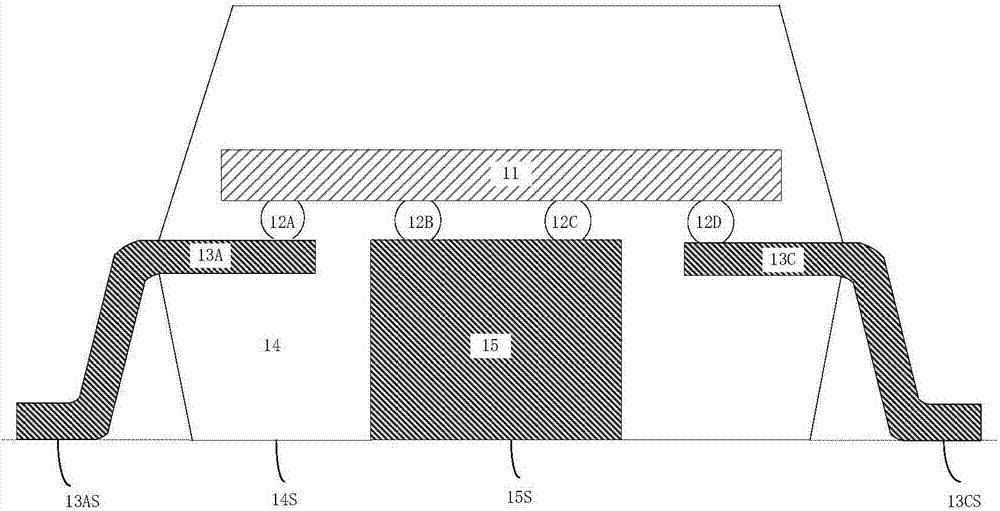

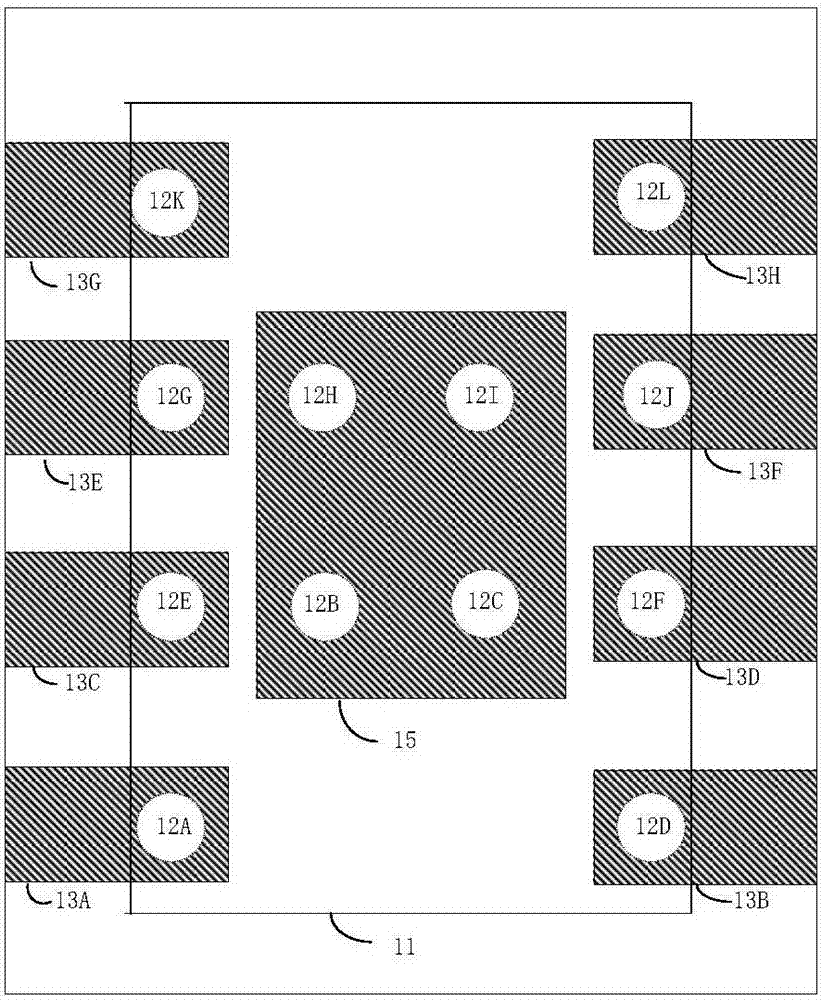

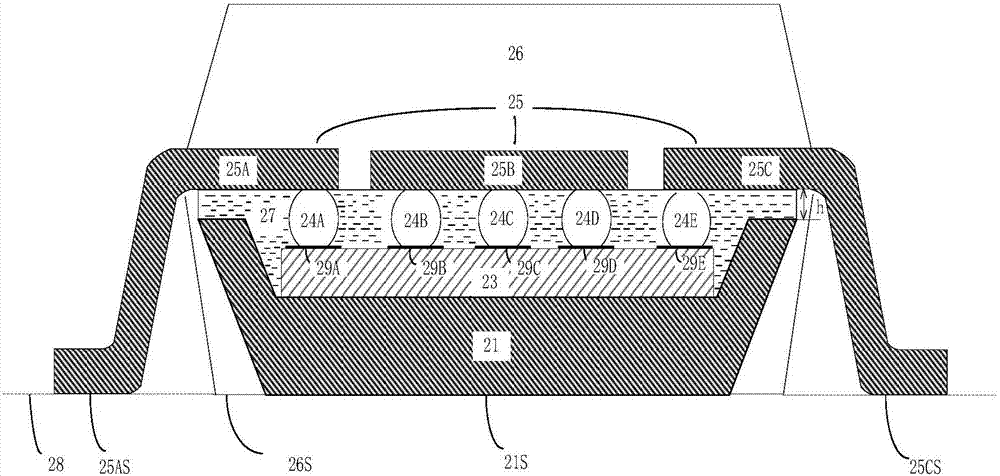

[0023] refer to image 3 , The flip-chip semiconductor packaging structure of the present invention includes: a lead frame 25 , a set of metal bumps 24A- 24E , an integrated circuit chip 23 , a heat sink block 21 and a molding compound 26 .

[0024] Lead frame 25 is provided with several pins that are insulated from each other. In this embodiment, three pins 25A-25C are taken as an example. The main surface of chip 23 is reserved with contact pads, and the contact pads are distributed according to the requirements of chip input and output signals. in the center and peripheral areas of the chip 23. The first metal bump 24A is planted on the chip 23 on the first contact pad 29A close to the first pin 25A, the second metal bump 24B is planted on the chip 23 on the second contact pad 29B close to the first pin 25A, The third metal bump 24C is planted on the third contact pad 29C in the middle area on the chip 23, the fourth metal bump 24D is planted on the fourth contact pad 29D ...

Embodiment 2

[0033] The structural relationship of this embodiment is the same as that of Embodiment 1, the difference is that the shapes of the cooling block and the groove are different, and the shape and structure of the cooling block and the groove are as follows: Figure 4 shown. The shape of the cooling block 31 in this example is a cuboid, and the shape of the groove is a step. The area of the bottom surface 30 in the step groove is smaller than the area of the backside of the chip.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thermal conductivity | aaaaa | aaaaa |

| Volume resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com