Half-rate clock data recovery circuit

A clock data recovery and half-rate technology, which is applied to logic circuits with logic functions, electrical components, digital transmission systems, etc., can solve the problem that the sampling position deviates from the optimal sampling point, the eye diagram of the input signal is not an ideal symmetrical shape, and the data Increased error rate and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] Embodiments of the present invention will be described below in conjunction with related figures. In the drawings, the same reference numerals indicate the same or similar components or method flows.

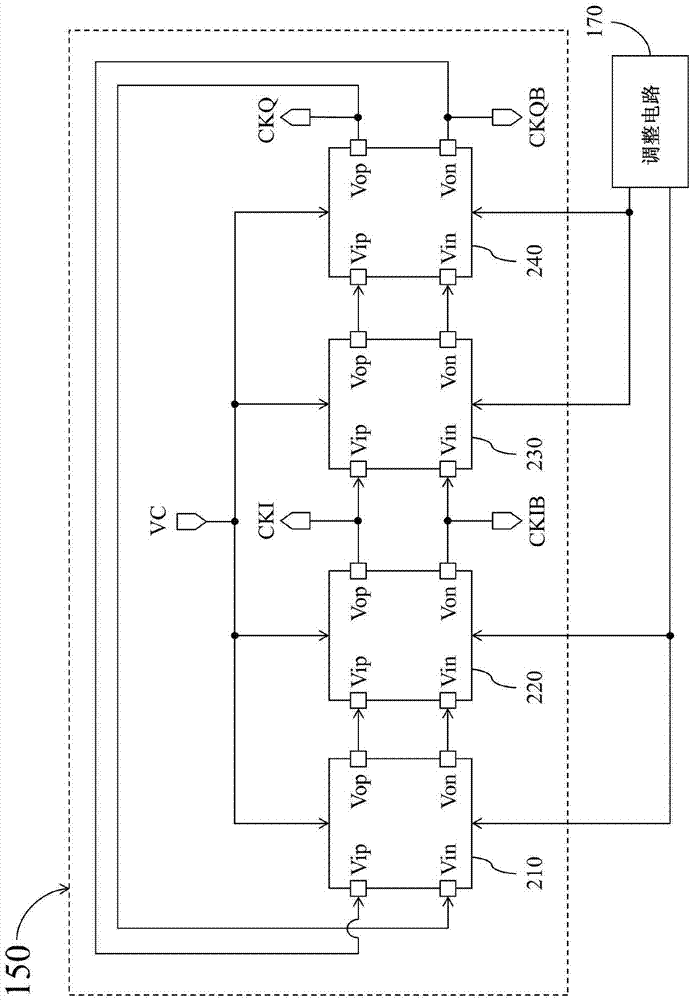

[0012] figure 1 It is a simplified functional block diagram of a half-rate clock data recovery circuit (half-rate clock data recovery circuit) 100 according to an embodiment of the present invention. The half rate clock data recovery circuit 100 is used to provide a clock data signal (clock data signal) DOUT to a data processing circuit (data processing circuit) 102 . like figure 1 As shown, the half rate clock data recovery circuit 100 includes a control voltage generation circuit 110, a data sampling circuit 120, an edge sampling circuit 130, a phase detection circuit 140, a voltage controlled oscillator 150, a frequency detection circuit 160, a The adjustment circuit 170 , a control circuit 180 , and a storage device 190 .

[0013] In the half rate clock data recov...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com