Vertical double-diffused metal oxide semiconductor device and fabrication method therefor

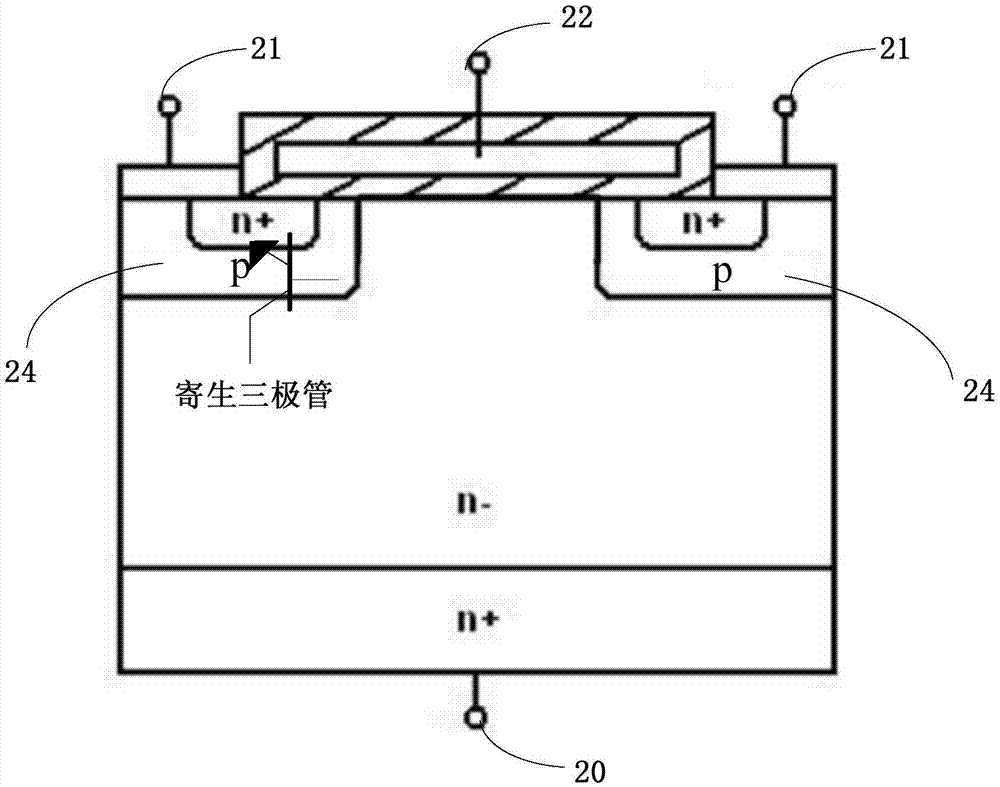

An oxide semiconductor and vertical double-diffusion technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve the problems of low avalanche energy of devices and easy opening of parasitic triodes, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

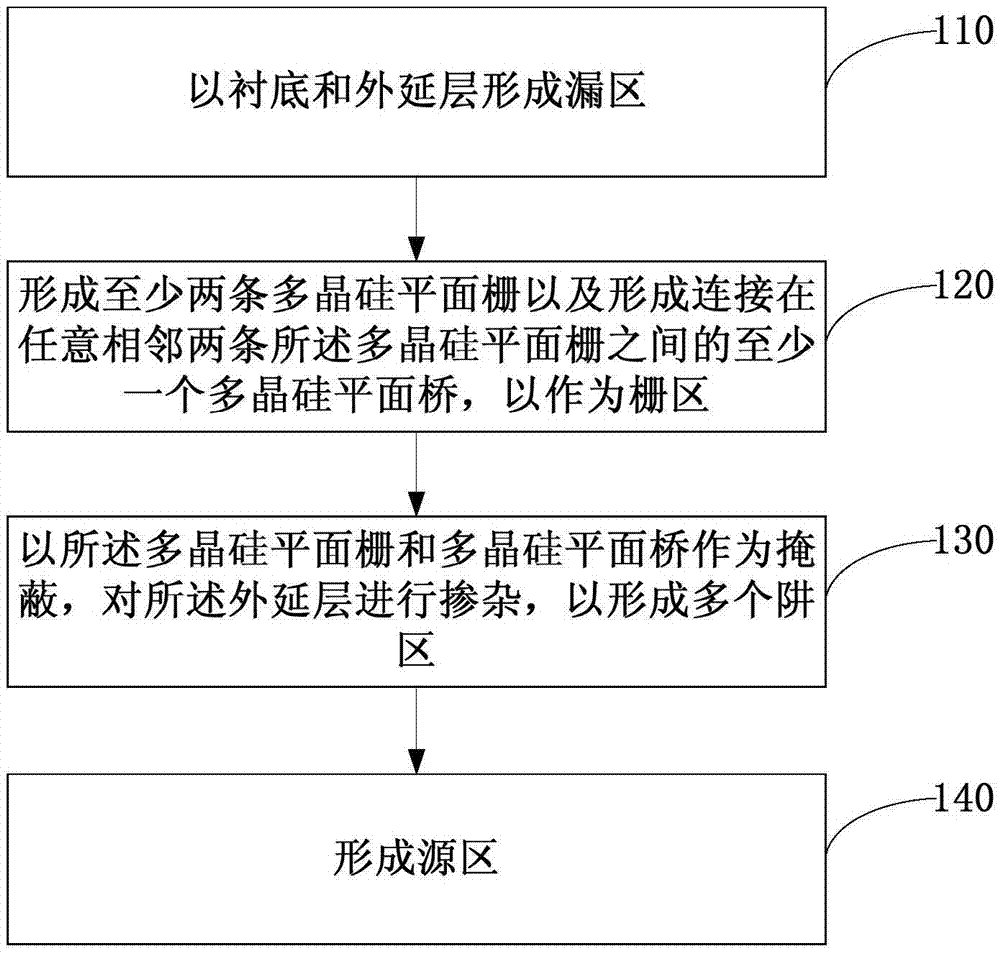

[0031] figure 2 It is a flow chart of a method for manufacturing a vertical double-diffused metal oxide semiconductor device provided in Embodiment 1 of the present invention. The method specifically includes the following steps:

[0032] Step 110, forming a drain region with the substrate and the epitaxial layer.

[0033] Taking an N-channel vertical double-diffused metal oxide semiconductor device as an example, an N-type epitaxial layer is fabricated on an N+ substrate, and the N+ type substrate and the N-type epitaxial layer are used as a drain region.

[0034] Step 120 , forming at least two polysilicon planar gates and forming at least one polysilicon planar bridge connected between any two adjacent polysilicon planar gates as gate regions.

[0035] Specifically, the polysilicon planar bridge includes two left and right strip structures connected to the polysilicon planar gate. Preferably, the center area of the polysilicon planar bridge is strip-shaped, circular or ...

Embodiment 2

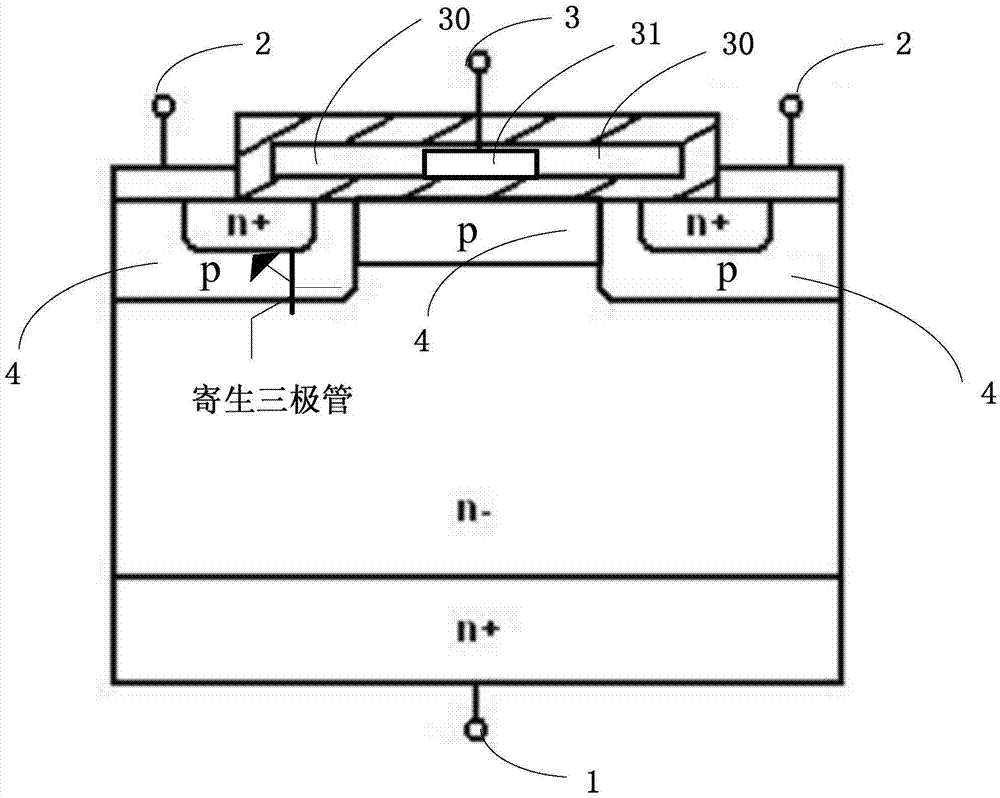

[0045] image 3 A schematic structural diagram of a vertical double-diffused metal-oxide-semiconductor device provided by Embodiment 2 of the present invention. The structure of the vertical double-diffused metal oxide semiconductor device includes: a drain region 1, a source region 2 and a gate region 3, and the gate region 3 includes:

[0046] At least two polysilicon planar gates 30, and at least one polysilicon planar bridge 31 connected between any adjacent two polysilicon planar gates.

[0047] Taking an N-channel vertical double-diffused metal oxide semiconductor device as an example, after the gate region 3 is formed, preferably, the vertical double-diffused metal oxide semiconductor device further includes: using the polysilicon planar gate 30 and the polysilicon planar bridge 31 as A plurality of well regions 4 formed after doping the epitaxial layer N- is masked, preferably, the well regions 4 are P well regions.

[0048] image 3 The parasitic triode is shown, b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com