Semiconductor element and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems affecting the integrity of spacers and complicated manufacturing process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] Although the present invention is disclosed as follows with the embodiment, it is not intended to limit the present invention. Anyone familiar with this technology can make some changes and modifications without departing from the spirit and scope of the present invention. Therefore, the protection of the present invention The scope should be defined by the appended claims, and in order to simplify the description, the details of some existing structures and manufacturing process steps will not be disclosed here.

[0043] Likewise, the figures shown are schematic diagrams of devices in the embodiments but are not intended to limit the size of the devices. In particular, in order to make the present invention more clearly presented, the sizes of some components may be enlarged in the figures. Furthermore, the same components disclosed in multiple embodiments will be marked with the same or similar symbols to make the description easier and clearer.

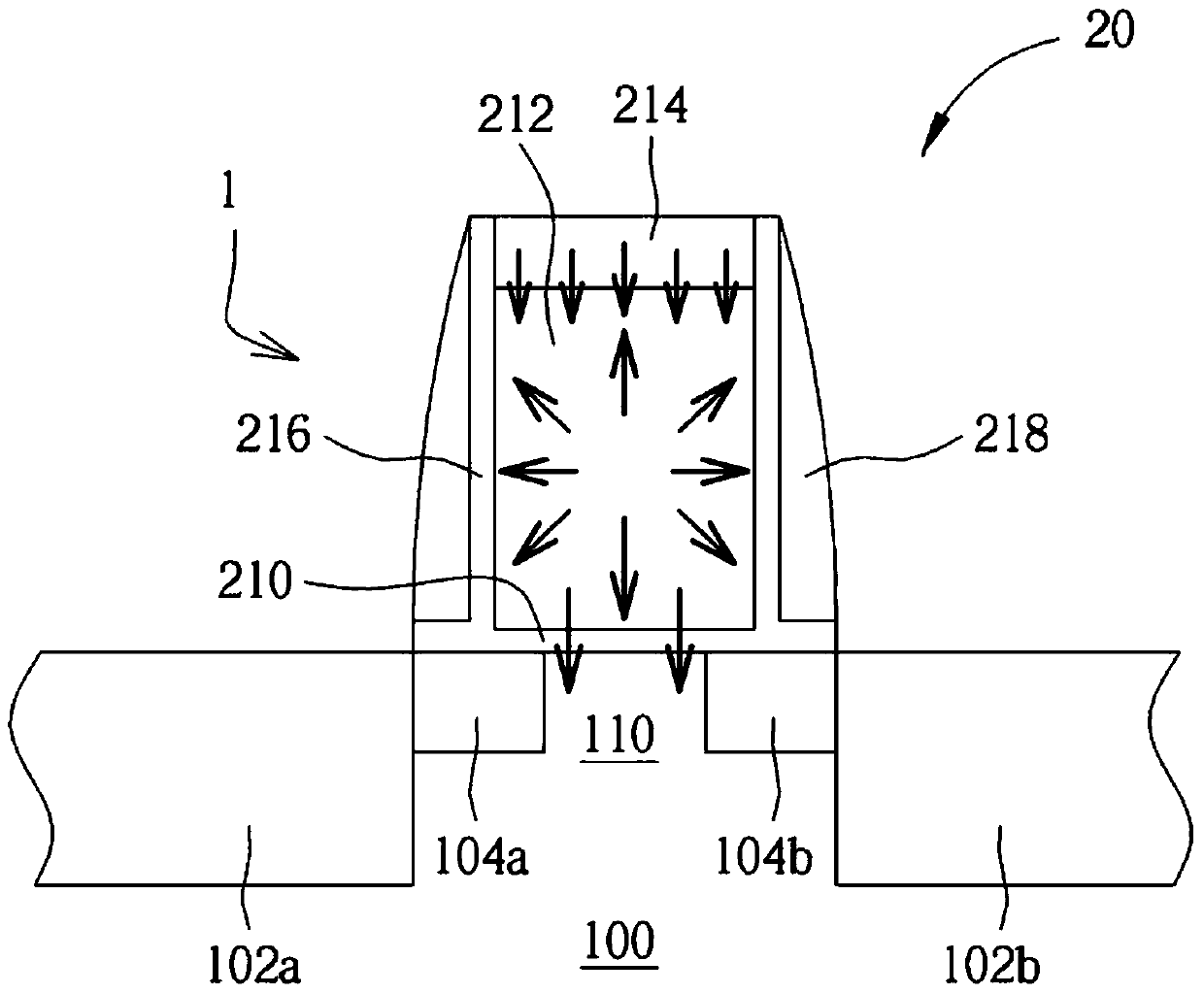

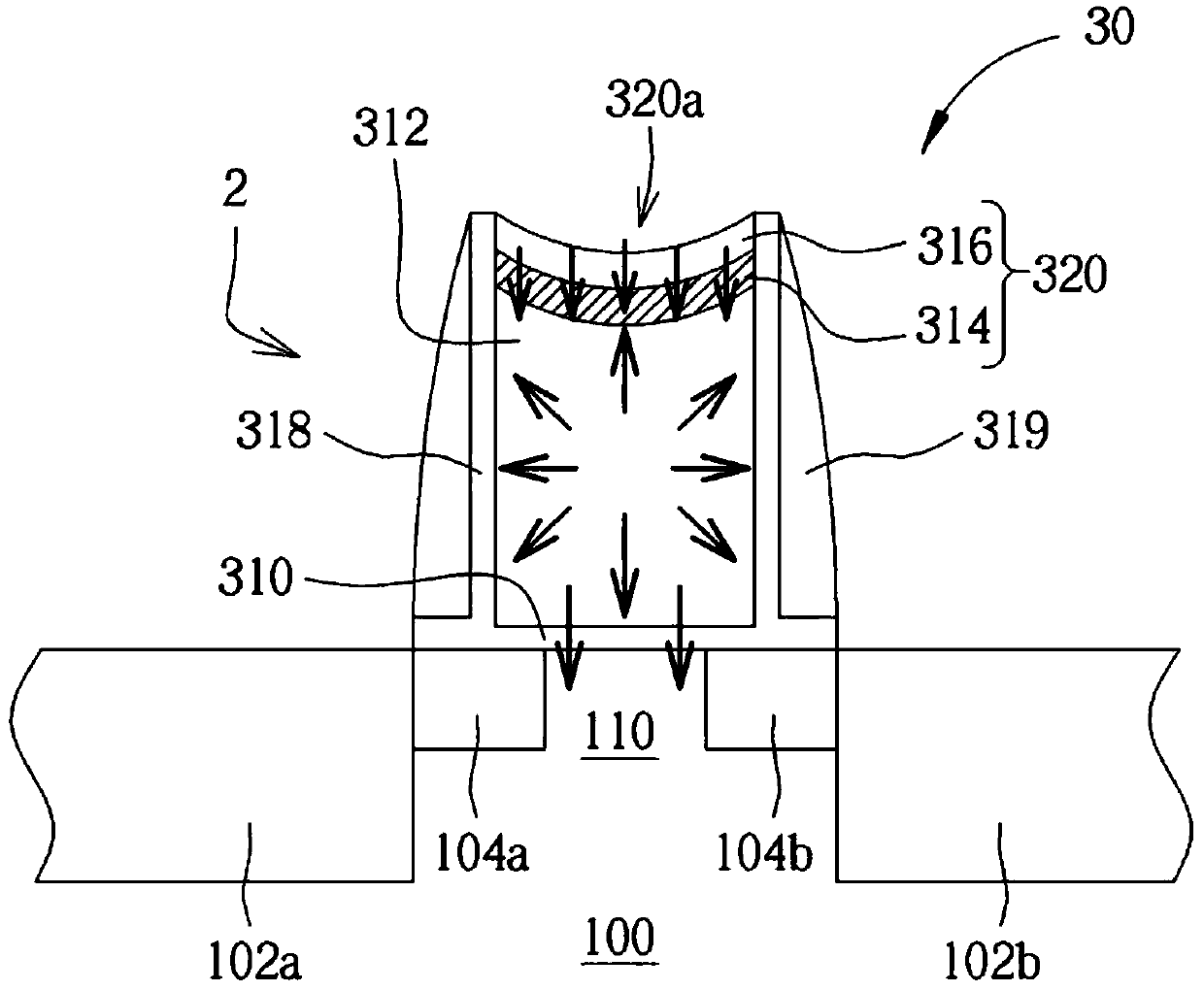

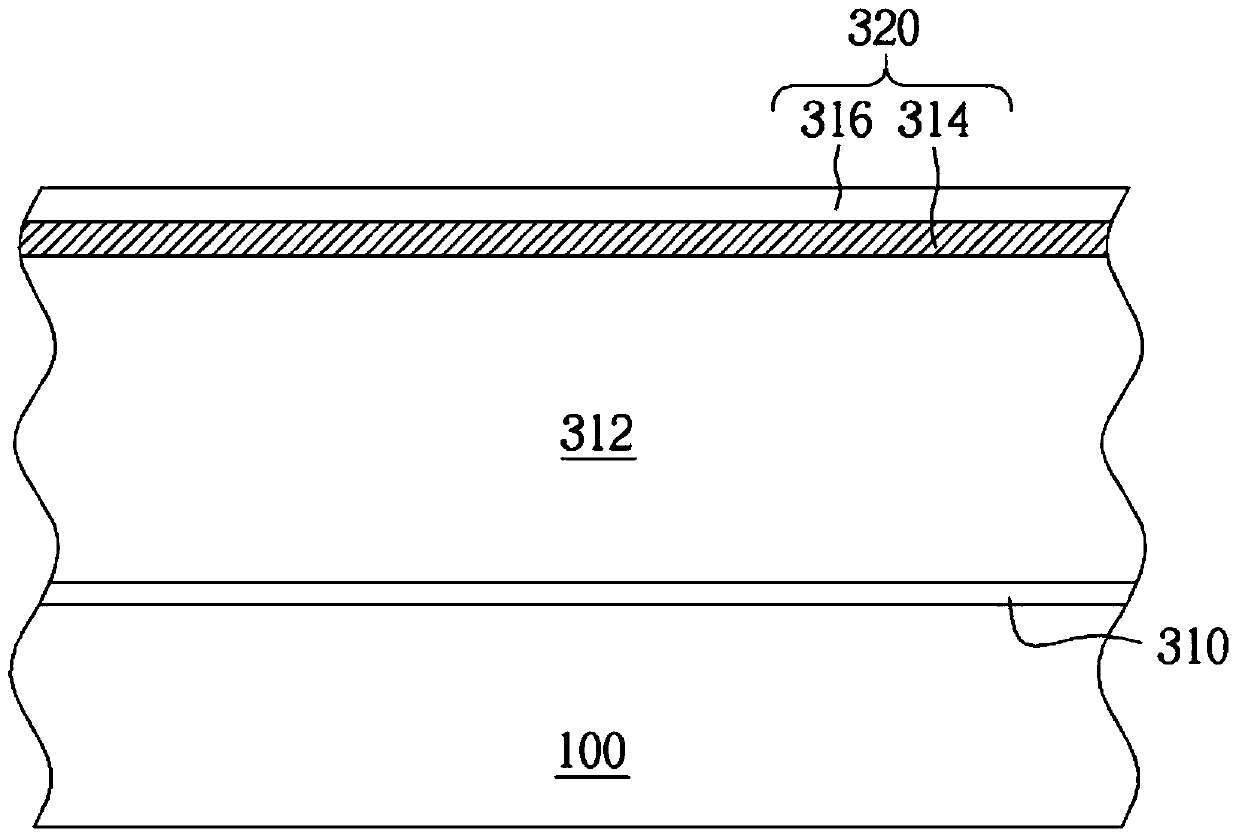

[0044] see figure 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com