Simulation design method for AC coupling capacitor reference plane

A technology of coupling capacitance and simulation design, applied in computing, electrical digital data processing, special data processing applications, etc., can solve problems such as impedance discontinuity, affecting link performance, affecting signal link insertion loss, etc., to ensure continuous impedance High reliability, operability, and space-saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

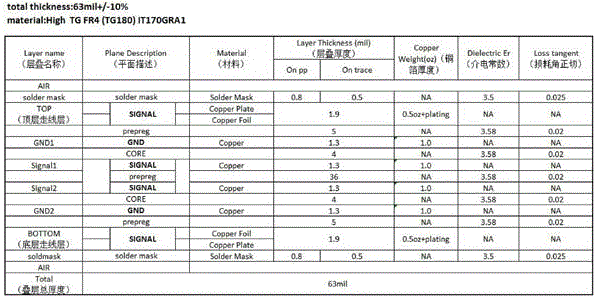

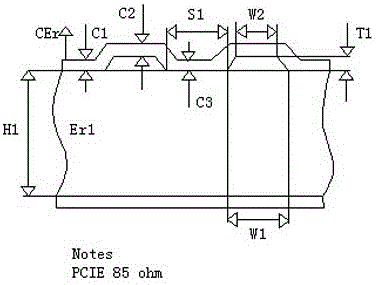

[0058] The simulated stackup adopts the attached figure 1 6-layer board shown, differential line impedance as attached figure 2 As shown, the capacitor is placed on the Top layer, referring to the GND of the second layer and the first reference layer. Hollow out the L2_GND first reference layer under the capacitor pad, and the capacitor pad will refer to the L3_first dielectric layer.

[0059] The capacitance information selected for simulation is as follows:

[0060] Capacitor size: 0402

[0061] Pad size: 18X22mil

[0062] Capacitor value: 0.01uf

[0063]Digging hole size: larger than the pad and so on, gradually increase by 2mil until the bottom of the capacitor is hollowed out as a whole.

[0064] Differential line impedance: 85ohmPCIE

[0065] Tracewidth: 8.3mil

[0066] TraceSpacing: 5.7mil

[0067] The emulation scheme that the present invention adopts is:

[0068] Construct the PCB model, use Sigrity PowerSI to extract the PCBS parameters, and then import the...

Embodiment 2

[0090] Further, a printed circuit board PCB includes a GND first reference layer, a GND second reference layer, a first dielectric layer, a second dielectric layer, a Top layer and a Bottom layer, and a signal transmission link, and the signal The transmission link is installed on the Top layer;

[0091] Wherein, the signal transmission link includes: two transmission lines and an alternating current AC coupling capacitor module, wherein the two transmission lines are connected through the AC coupling capacitor module;

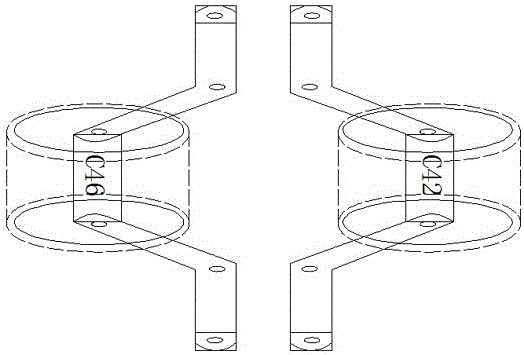

[0092] The GND first reference layer is provided with an impedance hole, and the opening area of the impedance hole is enlarged by 4mil for the projection area of the AC coupling capacitor module projected on the GND first reference layer in a positive projection mode. The shape of the aperture area is a longitudinal ellipse.

[0093] The signal transmission link includes: two transmission lines and an AC coupling capacitor module, wherein the two transmi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com