Reconfigurable signal processor ASIC architecture and reconfiguration method thereof

A technology of signal processors and registers, applied in the architecture with a single central processing unit, electrical digital data processing, instruments, etc., can solve the problems of single ASIC application environment, poor applicability, processor power consumption, area, and time , to achieve a wide range of applications, low power consumption, and easy to use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

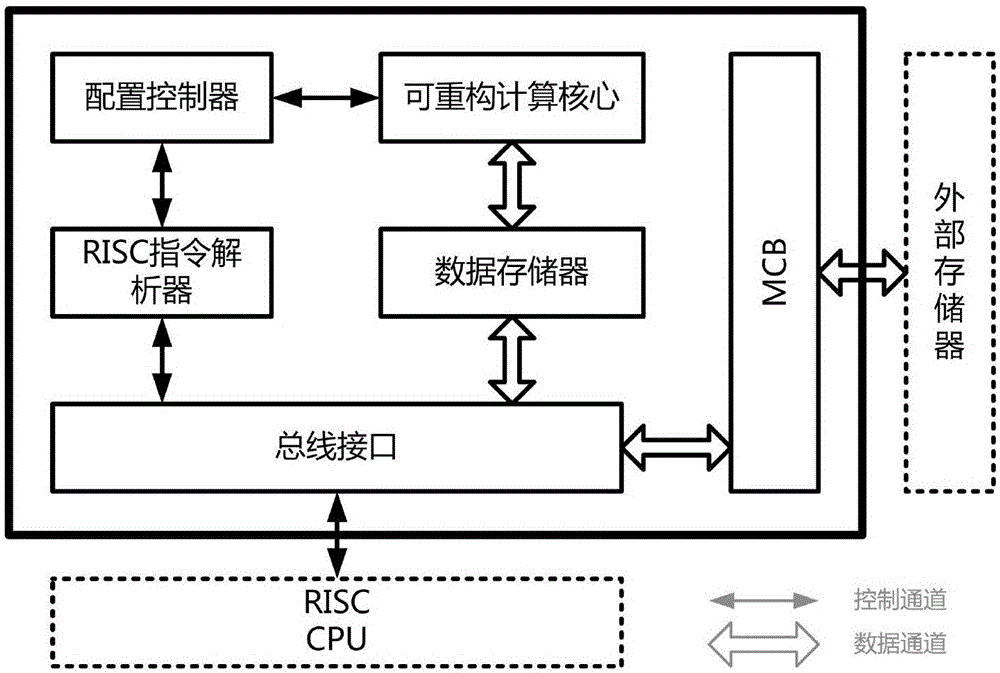

[0033] Such as figure 1 As shown, a reconfigurable signal processor ASIC architecture includes: RISC instruction parser, configuration controller, reconfigurable computing core, data memory, MCB (Memory Controller Block English abbreviation, meaning storage controller) and bus interface; the bus interface, RISC instruction parser, configuration controller and reconfigurable computing core are sequentially connected through the control bus to form a control channel, and the bus interface, MCB, data storage and reconfigurable computing core are sequentially connected through the data bus to form a data aisle.

[0034] The RISC instruction parser includes working status registers and configuration registers inside. Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com