Failure analysis method

A failure analysis and failure point technology, applied in electronic circuit testing, measuring devices, instruments, etc., can solve problems such as chip damage, tweezers bruises, scratches, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

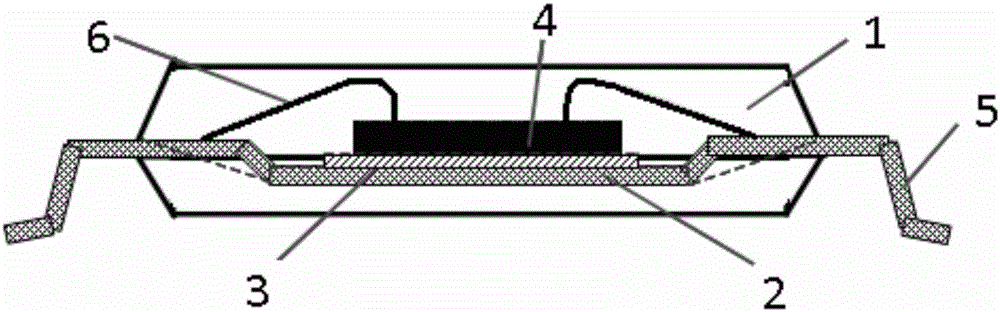

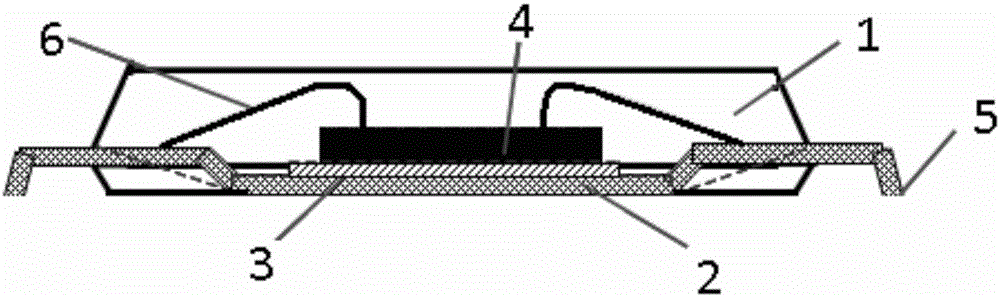

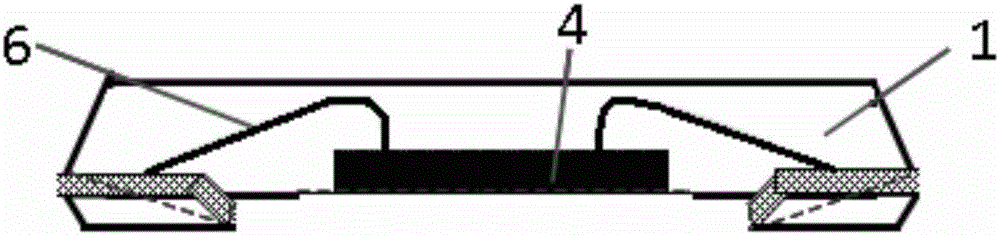

[0035] Figure 2 to Figure 4 Schematically shows the structure diagram of each step of the failure analysis method according to the preferred embodiment of the present invention. The failure analysis method according to the preferred embodiment of the present invention can be used for failure analysis of integrated circuit chip samples.

[0036] Specifically, as Figure 2 to Figure 4 As shown, the failure analysis method according to the preferred embodiment of the present invention includes:

[0037] The first step: grinding the packaging glue 1 on the back side of the packaging sample until the chip pad 2 is exposed;

[0038] Specifically, generally, the encapsulation glue 1 is encapsulation black glue.

[0039] For example, if figure 1 A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com