Delay performance test method and test device for fractional delay filter

A fractional delay and test method technology, applied in measurement devices, electronic circuit testing, instruments, etc., can solve the problems of high cost of analog delay lines, restricting the application of array radar, and receiving beam pointing offset.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] The method for testing the delay performance of the fractional delay filter of the present invention can be implemented in the FPGA, and directly reflects the fractional delay performance of the hardware. Fractional delay filter delay performance test method can be implemented in the form of software App, designed as a fractional delay filter delay performance test device, so that it can be conveniently implemented in electronic equipment with intelligent control. In addition, it can also It can be programmed into the control chip.

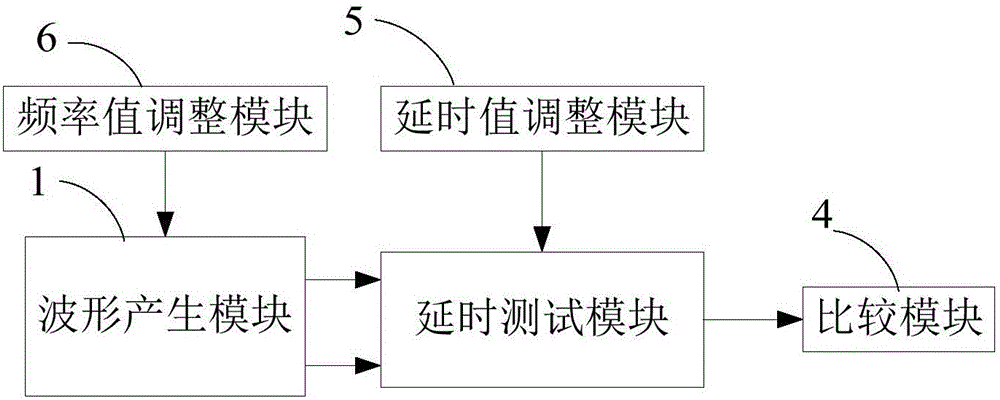

[0045] Please also refer to figure 1 and figure 2 , the fractional delay filter delay performance testing method of the present embodiment comprises the following steps, and the fractional delay filter delay performance test device corresponding thereto simultaneously comprises a waveform generation module 1, a delay test module, a comparison module 4, a delay A time value adjustment module 5 and a frequency value adjustment module 6 . ...

Embodiment 2

[0059] Please also refer to image 3 and Figure 4 , the fractional delay filter delay performance test method of the present embodiment and the fractional delay filter delay performance test device applying the method are basically the same as the method and device of embodiment 1, and the difference is that: embodiment 1 Steps S12 and S13 run synchronously, so Embodiment 2 can test two fractional delay filters to be tested.

[0060] Therefore, in the second step S12, the test signal one is sent into a fractional delay filter to be tested with a delay value set to zero, and thus an output signal one is formed; and in the third step S13, the The test signal 2 is sent to another fractional delay filter to be tested whose delay value is set to the delay accuracy value, and the output signal 2 is thus formed; then the corresponding two fractional delay filters to be tested are evaluated in subsequent steps The delay performance of the device.

[0061] That is, the delay test m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com